you're theorizing, in theory we 100% agree

I'm also only talking mobile

however the reality is that STX completely failed.

STX (4p8c hybrid) vs 9955HX (full 16p) = STX loses literally everywhere from 5% to 70% or so

even gaming: both FHD and QHD, 9955HX squeezes from +15 to +60 fps... same GPU + TDP

STX laptops are also so expensive that it's hard to justify vs 9955HX unless you need a specific model for whatever reason unrelated to CPU (i.e. 4k screen unavailable to 9955HX models)

the only remaining theory is 4p+8c doing better than full CCD in ultramobile/lowTDP situations, but even there STX gets trashed..... in all scenarios, both low and high power

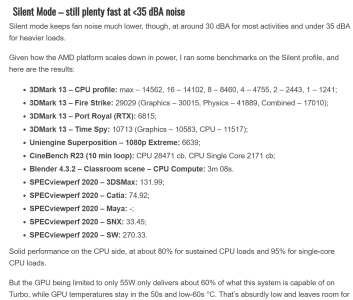

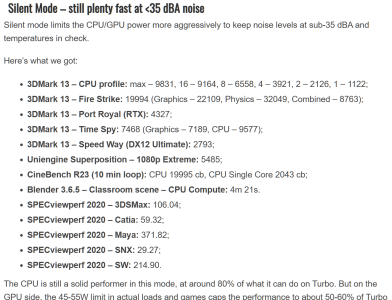

compare the CPUs with same GPUs on silent mode

asus strix G16 (9955HX + 5070ti):

View attachment 136130

asus zephyrus G14 (STX + 5070ti)

View attachment 136129

huge difference.......

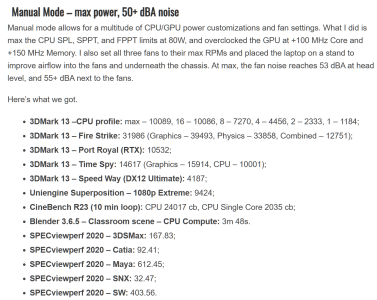

also, 9955HX silent (55W TGP GPU) hits blows with HX370 manual (max power, 50+dbA) on certain parts:

View attachment 136132

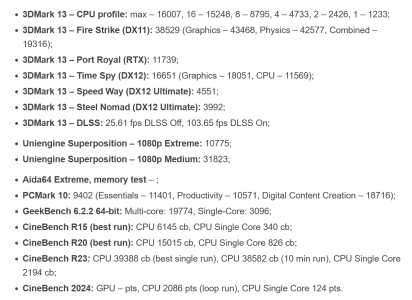

but all that gets completely owned by 9955HX turbo (manual can get extra +5%) :

View attachment 136133

all this is reflected in real games FPS too

farcry6 QHD ultra:

9955HX(silent) = 83fps

STX(silent) = 54fps

STX(perf) = 92fps

9955HX(perf) = 118fps

cyberpunk QHD ultra:

9955HX(turbo) = 84fps

STX(turbo) = 62fps

basically, silent 9955HX > performance (loud) STX...

literally silent 9955HX vs perf/loud STX HX370:

+50% Fire Strike score

+50% Cinebench MT,

+10% ST

+45% 3DMARK CPU score

~+25% SPECviewscore

with real games FPS being similar....

the links full reviews

lastly AMD has developed the ultra-low-power interconnect used on Halo but they didn't manage to fit it on 9955HX on time. zen6 should have it by default, makes 24 full cores viable to run on low power mode