Unified generally has better utilization, but requires more area and power than distributed scheduler.Is this a good or a bad thing? What does it mean for performance impacts do you think?

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Zen 6 Speculation Thread

Page 323 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

adroc_thurston

Diamond Member

yeah so you get a lot less entries.but requires more area and power than distributed scheduler.

In any case, this looks like it went back to Zen1/2 scheduler layout?

More like Zen3 imo. Zen3 had 4 schedulers (3x ALU + AGU, 1x ALU + Branch). I think Zen6 is 6x ALU + AGU.yeah so you get a lot less entries.

In any case, this looks like it went back to Zen1/2 scheduler layout?

Win2012R2

Golden Member

Will that improve integer perf substantially?I think Zen6 is 6x ALU + AGU.

adroc_thurston

Diamond Member

RETVRN TO K10.5I think Zen6 is 6x ALU + AGU.

no.Will that improve integer perf substantially?

while Zen5 math scheduler was kind of crowded, it's not the main limit.

You have front-end latency, ROB size and int prf to content with mostly.

Pretty sure Zen5 was the first Zen to run out of int regfile in games which is a bit funny.

Win2012R2

Golden Member

What will it improve then - FP or just more suitable for SMT workloads?

adroc_thurston

Diamond Member

Well it's the int scheduler.What will it improve then - FP or just more suitable for SMT workloads?

Idk how it impacts FP or SMT suitability.

adroc_thurston

Diamond Member

In any case, this is the first time AMD is diddling schedulers for a derived core.

Win2012R2

Golden Member

Well if it schedules better then int perf should go up, right? Seems like a drastic change which would be big risk if perf improvements were not goodWell it's the int scheduler.

adroc_thurston

Diamond Member

Maybe.Well if it schedules better then int perf should go up, right?

math scheduler capacity wasn't a big or real bottleneck for Zen5.

They can split schedulers for fmax reasons or for Cac reduction. Many many many different ways to slice it.

adroc_thurston

Diamond Member

oh okay memory scheduler is also GONE.

We're either back to Zen3/4 sched layout, or K10.5.

The latter is the funnier option.

We're either back to Zen3/4 sched layout, or K10.5.

The latter is the funnier option.

Nothingness

Diamond Member

This reminds me of Intel matrix scheduler: https://dl.acm.org/doi/pdf/10.1145/1273440.1250704

Not saying AMD are doing such an implementation, just that the unified scheduler discussion made me think about what Intel used to do (or still do?) 🙂

Not saying AMD are doing such an implementation, just that the unified scheduler discussion made me think about what Intel used to do (or still do?) 🙂

adroc_thurston

Diamond Member

ah no LNC ditched unified scheduler and also fixed the port favela that's been with us since P6.just that the unified scheduler discussion made me think about what Intel used to do (or still do?)

Didn't make the core any better, unfortunately.

CouncilorIrissa

Senior member

Grok, find team B's fingerprints on this change.

Cheesecake16

Member

Oh awesome, my speculation, at least for the integer scheduler, looks to likely be wrong and that's great!

I do love when I get shit wrong because that means I get to ask questions and learn more about why they did what they did... and I do like interesting twists and this is definitely an interesting twist...

adroc_thurston

Diamond Member

wanna bet on i$ size now?Oh awesome, my speculation, at least for the integer scheduler, looks to likely be wrong and that's great!

I do love when I get shit wrong because that means I get to ask questions and learn more about why they did what they did... and I do like interesting twists and this is definitely an interesting twist...

It's amazing how AMD, for the first time in its history, introduced a unified scheduler for 6 ALUs and a separate one for 4 AGUs in Zen5, only to return to the Zen4 scheduler in the next generation of Zen6. That means 6 schedulers, each supporting 1 ALU + 1 AGU, or most of them.

I'm curious about the entire Zen6 core and what other changes have been made compared to Zen5.

I'm curious about the entire Zen6 core and what other changes have been made compared to Zen5.

Cheesecake16

Member

I am really interested if they have added 2 more AGUs... because that would be up to 6 memory ops per cycle which is quite spicy IMO...oh okay memory scheduler is also GONE.

We're either back to Zen3/4 sched layout, or K10.5.

The latter is the funnier option.

I am going to assume it's the same 32KB as Zen 2-5 but I am kinda really hoping for 48+ KB... Maybe 64KB... maybe...wanna bet on i$ size now?

But by such a large margin though?Simple, you are having to feed a much larger frontend... you expect more L1i misses assuming the same structure size...

Do we have any reference to other architectures that kept the same L1i capacity but massively increased the front end? GLC vs SNC could be a good comparison, considering they also doubled the L1i bandwidth, kinda like Zen 5 due to the 2 ahead BP?

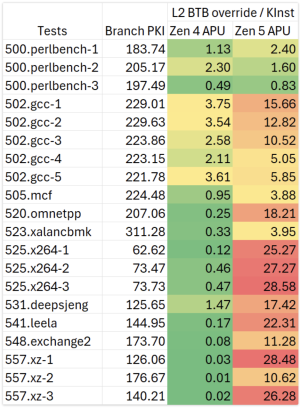

The only specint2017 subtest where L2 BTB overrides went down in Huang's testing was 500.perlbench 2. 500.perlbench 1 and 3, as well as all the other specint subtests he ran, saw a large L2 BTB override increase.So that is very dependent on the workload, for example compiling the Linux Kernel the L2 BTB overrides went down from about 12.86 MPKI to about 3 MPKI... where as the L1 iTLB misses went up which again isn't surprising considering that the L1 iTLB size didn't change from Zen 4 to Zen 5...

Maybe a double node jump allows them to increase capacity. Intel did increase L1i capacity from GLC to RWC when they shrunk from Intel 7 to Intel 4.I am going to assume it's the same 32KB as Zen 2-5 but I am kinda really hoping for 48+ KB... Maybe 64KB... maybe...

adroc_thurston

Diamond Member

oh nyo area isn't the problem.Maybe a double node jump allows them to increase capacity

They're just fmaxxing to the gills.

no. speed is life.Could it they are going back to previous designs because Zen6 is going to used in more client focused products as well?

😉In any case, this is the first time AMD is diddling schedulers for a derived core.

adroc_thurston

Diamond Member

Oshiete, eep-sempai

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-