-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Zen 6 Speculation Thread

Page 296 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

adroc_thurston

Diamond Member

Does it matter?To the group, isn't Venice dense looking like a huge chiplet?

CSPs can and will pay.

True.Does it matter?

CSPs can and will pay.

To the group, isn't Venice dense looking like a huge chiplet?

Maybe ~200 mm2? Could be below that.

techjunkie123

Member

My estimate is ~150 mm^2. Pretty manageable.To the group, isn't Venice dense looking like a huge chiplet?

Source: trustmebro™

That's not hard to guess or explain, and the only reason we're still having this discussion at all is because some people refuse to accept the reasons and explanations that have been given multiple times.Assuming that will be the case, why will they choose different policy for Zen6 vs Zen5? Why use different nodes per CPU type for Zen5 but not for Zen6? I assume there was some reason different nodes were used for Zen5.

In short, Zen5 was mostly an outlier because TSMC messed up the original N3.

It also was actually an all-N4P gen (with some 'X' transistors in the 8C CCD, allegedly), except one single N3E CCD, for a possibly area-constrained* product in a very high-margin market niche, where any cost/yield issues would've been relatively easy to absorb.

*Turin-D has 12 CCDs, and look at that package layout.

You think they could've fit those 12 CCDs on that if these CCDs were ~30% bigger?

Tricky at best, impossible at worst.

adroc_thurston

Diamond Member

Yeah.You think they could've fit those 12 CCDs on that if these CCDs were ~30% bigger?

It's on N3e for PPW buffs and also via being the least important product ever.

Josh128

Banned

Found this page at TSMCs website. I found this by doing a google search on differences between TSMC standard and HPC processes. Usually,

standard vs HPC means tradeoffs in density and/or leakage. It appears that there is little performance difference, and therefore presumably little density and

leakage differences, between N2P and N2.

www.tsmc.com

www.tsmc.com

standard vs HPC means tradeoffs in density and/or leakage. It appears that there is little performance difference, and therefore presumably little density and

leakage differences, between N2P and N2.

Advanced Technologies for HPC - Taiwan Semiconductor Manufacturing Company Limited

N5 is the next-generation technology after N7 that is optimized upfront for both mobile and HPC applications. It is defined with innovative scaling features to enhance logic, SRAM and analog density simultaneously. Compared with N7, N5 offers substantial power, performance and date density...

If that is what you really think (that providing reasoning in a speculation thread is useless) I guess we agree to disagree. The thread is about "tell us about leaks". It's speculation .... which begs the question of reasoning.Yes, given the circumstances (replying to a leaker that can't/won't verify his sources, or in the case of Venice being in the hand of cloud service providers, ignoring/forgetting that Dr. Su already told us that Venice is in the hands of cloud service providers. Likely AO silicon).

luro

Member

I think that’s what we expected alreadyVenice D on N2P

I still think it's base N2 and not N2P, being pedantic.I think that’s what we expected already

I think only the eoy 2026 products are going to be N2P.

I'm expecting MI400 too to be on N2 and not N2P.

Internally they call it N2P but either way it's not bog standard TSMC N2 or N2P.I still think it's base N2 and not N2P, being pedantic.

I think only the eoy 2026 products are going to be N2P.

I'm expecting MI400 too to be on N2 and not N2P.

You do know that the PDK for N2/N2P are the same just there is difference between process flow and as for bog standard the PDK has many options.Internally they call it N2P but either way it's not bog standard TSMC N2 or N2P.

poke01

Diamond Member

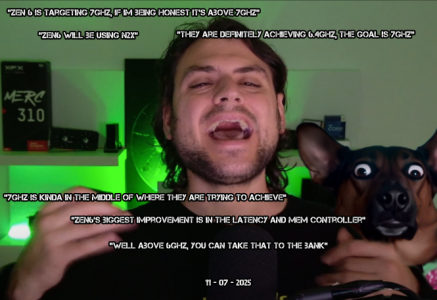

N2X was never on the cards. and 7GHz is a meme. It won't happen, N2 is good but not THAT good.

adroc_thurston

Diamond Member

Stop talking stuff about foundry partnerships you can't comprehend.N2X was never on the cards. and 7GHz is a meme. It won't happen, N2 is good but not THAT good.

Gideon

Platinum Member

BTW, do you guys think we will get any substantial info on today's Financial Analyst Day?

I just looked at the slides from the 2022 event, and while there definitely will be some info, it's better not to hope for too much.

The event was on June 9, 2022, and we got:

Unfortunately, considering the crazy focus on AI, today's event might talk much less about CPUs to begin with.

My guess is we'll be lucky to get any info about Zen 7 (even as little as there was about Zen 5 in 2022), but there should be at least some hard metrics regarding Zen 6. I doubt we'll get exact IPC/Clock numbers, though. It's way too far out compared to the three months (for Zen 4) in 2022.

I just looked at the slides from the 2022 event, and while there definitely will be some info, it's better not to hope for too much.

The event was on June 9, 2022, and we got:

- Updated mobile roadmap that very briefly mentioned Phoenix Point and Strix point:

- A bit more info about Zen 4 that was just three months away ( arrived September 2022):

- A similar low-granularity desktop Roadmap:

Unfortunately, considering the crazy focus on AI, today's event might talk much less about CPUs to begin with.

My guess is we'll be lucky to get any info about Zen 7 (even as little as there was about Zen 5 in 2022), but there should be at least some hard metrics regarding Zen 6. I doubt we'll get exact IPC/Clock numbers, though. It's way too far out compared to the three months (for Zen 4) in 2022.

poke01

Diamond Member

love it when internet randos tell people what to say or don't sayStop talking stuff about foundry partnerships you can't comprehend.

The partnership may be in advance but you can't ship something before it's ready .Stop talking stuff about foundry partnerships you can't comprehend.

adroc_thurston

Diamond Member

Trvkelove it when internet randos tell people what to say or don't say

Ready is a vague term here.The partnership may be in advance but you can't ship something before it's ready .

But reasoning was provided, you only missed it or keep ignoring it: It is implied (most of the time; occasionally it was explicitly said so) that the poster claims to know this. This is the entire reasoning. Nothing more.If that is what you really think (that providing reasoning in a speculation thread is useless) I guess we agree to disagree.

You don't have to believe that the poster knows it, nor do you have to believe that the poster understood exactly what he heard if he actually heard anything. But what would be beneficial to the signal-to-noise ratio of this thread is that you realize that the reasoning for which you asked is already there, and there is nothing more beyond this.

I think there will be decent amount of info on Zen6 and MI450, some stuff on RDNA5/next-gen consoles and maybe some vague info on Zen7 and MI500.BTW, do you guys think we will get any substantial info on today's Financial Analyst Day?

I just looked at the slides from the 2022 event, and while there definitely will be some info, it's better not to hope for too much.

The event was on June 9, 2022, and we got:

- Updated mobile roadmap that very briefly mentioned Phoenix Point and Strix point:

- A bit more info about Zen 4 that was just three months away ( arrived September 2022):

- A similar low-granularity desktop Roadmap:

Unfortunately, considering the crazy focus on AI, today's event might talk much less about CPUs to begin with.

My guess is we'll be lucky to get any info about Zen 7 (even as little as there was about Zen 5 in 2022), but there should be at least some hard metrics regarding Zen 6. I doubt we'll get exact IPC/Clock numbers, though. It's way too far out compared to the three months (for Zen 4) in 2022.

adroc_thurston

Diamond Member

Yuo forgot networking talk.I think there will be decent amount of info on Zen6 and MI450, some stuff on RDNA5/next-gen consoles and maybe some vague info on Zen7 and MI500.

HVM Ready*Ready is a vague term here.

[x86 core roadmap rumor from September 29, 2023]

________

¹) though since Zen 5, with the microarchitectural option of either 256 bits or 512 bits FP datapaths, both in classic and dense

While classic and dense are the same microarchitecture¹, there were speculations that the low-power core option would be provided as a cut-down microarchitecture. If Zen 6 based mobile SoCs will feature such LP cores with a dedicated reduced microarchitecture, then it is possible that the LP µarch ends up being closer to Zen 5 than to Zen 6. That said, how AMD is going to call such a microarchitecture publicly is another topic.At this point the slide has been absolutely proven legit [...] The " New Low power core" option was given starting at Zen 5, and it never saw the light of day, but that just means they chose not to deploy it then. We now believe Zen 6 comes with it.

________

¹) though since Zen 5, with the microarchitectural option of either 256 bits or 512 bits FP datapaths, both in classic and dense

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-