CouncilorIrissa

Senior member

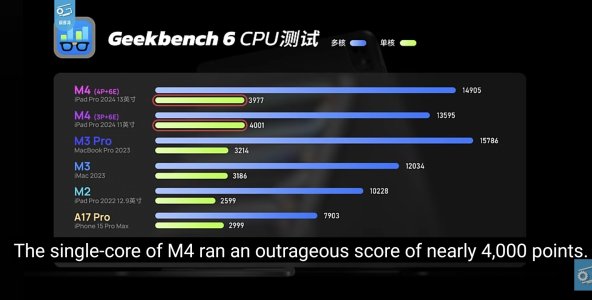

Embarrassing for the two oldest CPU manufacturers to be gapped by them in such a fashion.It's incredible that Apple and Arm are able to do IPC/Performance gains almost every year while Intel, AMD and QCOM are roughly on a 18 months cadence. And sometimes the latter 3 might not even bring a good performance uplift.