Darkmont

Member

Total Nuvia supremacyAnd to hell with it, NVL loses to Glymur let alone Z6, Intel is a banana republic.

Total Nuvia supremacyAnd to hell with it, NVL loses to Glymur let alone Z6, Intel is a banana republic.

Yes, but A16 may not offer enough of a benefit over N2 to justify an entire family design change. Moving forward, it may require a double die shrink to make it worthwhile to move to a new process, and thus a new generation of processors.

Processors are only redesigned when transistor budget increases provide a path to meaningful improvements to the product. When a single die shrink offered double the transistor budget, this was a no brainer. When a single die shrink offers 10-15% higher transistor density ..... and costs 30-50% more? Not so much.

I feel many people here overlook (or don't agree) that this is true and that from one generation to another, just using the same transistor budget, but doing it more cleverly, will give you very meaningful gains. I just don't believe this is true. I think it requires more transistors to give meaningful gains in processing.

What matters is the ASP of the main margin additive part.

For Z4 it was $450, Z5 $480 and Z6 it's gonna be $600.

Total Nuvia supremacy

Currently AMD is winning the high end of nearly every market in x86 and thus is raking in all the gravy.What matters is the ASP of the main margin additive part.

For Z4 it was $450, Z5 $480 and Z6 it's gonna be $600.

That more than overcomes the BOM increase, N2P is the right call and volumes will be similar in time, which means more revenue and more GM than prior generations.

This is exactly what NV has done for each generation since Maxwell with a short break for Ampere (node was dirt cheap so GMs were still very good), it works when you win and can only be stopped when you lose.

And to hell with it, NVL loses to Glymur let alone Z6, Intel is a banana republic.

I wonder if "the juice is worth the squeeze" though. Why go through an entire development cycle, pay for higher production costs for a product that gains you ~10% over the previous product?It's incremental. Incremental improvement to CPU / GPU designs, incremental improvement to process technologies.

It seems that (coincidently?) the cadence may be converging, between CPU generations and new process technology nodes.

What if AMD can do that (as it is today) AND not use the leading and most expensive node to do it?Yup, Change in ASP in dollar terms dwarfs the change in BOM in dollar terms.

There is another scenario where ASPs don't have to change very much, that can still absorb the increased BOM. Consider this scenario:

- AMD moves to more advanced node, which increases BOM

- as a result of advanced node, AMD sells more CPUs, because they are more attractive

- as a result of selling more CPUs, design costs are spread over larger number of CPUs

- resulting in design cost per CPU going down

- lower design cost per CPU can offset increased BOM

Currently AMD is winning the high end of nearly every market in x86 and thus is raking in all the gravy.

As long as AMD maintains a performance advantage (and power advantage in some cases), they will maintain this market.

Holding the market position doesn't determine the price of a position within that market. The top end of the desktop market is still $500-$700. It doesn't matter that Zen 6 may be 25% faster than Zen 5. It doesn't become 25% more expensive. This is NOT how the market works.

Should AMD dominate sales in the higher margin areas, they will still wish to expand into the lower margin, higher volume markets. In these markets, cost plays a huge role. This is where N3P would make more sense than N2.

I wonder if "the juice is worth the squeeze" though. Why go through an entire development cycle, pay for higher production costs for a product that gains you ~10% over the previous product?

I also think that the answer to that question largely depends on your position in the competitive market. If AMD can dominate with a less expensive node (like they are today), how would it make any sense to use a more expensive node?

Am I the only person here old enough to remember the stagnation we had with Intel when AMD was not competitive?

I have been an AMD fan for decades. Still, I am no fool. Should AMD become dominant, and Intel offers no reasonable competition, the top end will stagnate.

I think for OEM sales, Intel has a huge history of package deals and just general know-how in that market that AMD is just starting to learn. On the other hand, DIY has been AMD's bread and butter for decades.Not on the client. Still in 20% range market share in both desktop and clients. There is a plenty of room to double that.

I still see a ton of Arrow Lake 285 on Dell site. So AMD does not have enough of high end even in desktop.

In notebooks, AMD has minimum high end penetration. Servers is the only area where AMD dominates the high end.

No argument. I think that supplying the larger market, lower margin products to OEM's requires a certain combination of product mix, OEM interaction processes, and volumes of scale AMD is not currently adept at.The goal is to increase the gap, not just maintain it, which would then enable faster shift in market shares.

In theory, AMD share can go up 4x, and at the end, the state of x86 would be the same, except the players would flip their 80:20 to 20:80

Agree.I think the mistake you are making is overestimating AMD penetration in client. DIY is not representative of the whole client. There is room, in client, for massive market share gains.

I think for decades, the deck was stacked in Intel's favor in commercial client. The old guard dies hard.Lack of success penetrating in notebook space and limited success in commercial client does not equal to lack of ambition.

It just means the stars were not aligned yet to allow this to happen

I think for OEM sales, Intel has a huge history of package deals and just general know-how in that market that AMD is just starting to learn. On the other hand, DIY has been AMD's bread and butter for decades.

I am not certain that AMD's success and experience in DC translates well into consumer OEM. I feel they still have lots to learn for this market and it is this learning that holds them back, not the product lineup.

No argument. I think that supplying the larger market, lower margin products to OEM's requires a certain combination of product mix, OEM interaction processes, and volumes of scale AMD is not currently adept at.

Agree.

I think for decades, the deck was stacked in Intel's favor in commercial client. The old guard dies hard.

Those are expensive specialty parts.with chiplet Zen 6 and RDNA5 parts

Those are expensive specialty parts.

Actual Zen6 lineup is all RDNA3.5.

Nope you go straight to Zen7 APUs.there would be a good reason to refresh MDS1 die from RDNA3.5 + NPU -> RDNA5

Yeah it's called MI400.I wonder what (if any answer) AMD has for Intel AMX

Nope you go straight to Zen7 APUs.

Yeah it's called MI400.

I wonder what (if any answer) AMD has for Intel AMX. I wonder if or when we could see AMX and APX in Zen CPUs. Probably not Zen 6

AMD already announced that Zen 7 will be released in 2027 with the MI500 series.If the cadence is now 24 months+ (with Zen 6) and then, projecting the same to Zen 7, there is more than enough time for a refresh that is this meaningful.

AMD already announced that Zen 7 will be released in 2027 with the MI500 series.

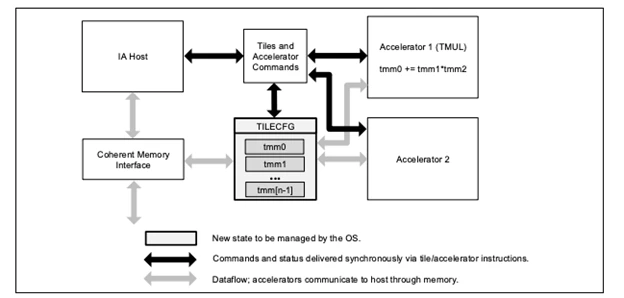

View attachment 131022

Looking at this I do not see the need or any reason to include the AMX units in the "IA" host.

If AMD wants AMX from Intel, they'll probably do it with some weird glue.

If they include enough, it'll put the Zen team in some competition with MI. Maybe they'll do it anyway.

Zen 6 architecturally is not a big step forward (relative to anyone except Intel P core). Each and every part depends on physical design and implementation to achieve competitive frequency in its target market. If it ships after July 2026, they really need to re-Zen themselves.If the cadence is now 24 months+ (with Zen 6)

Based on a little reading and research, AMX is only interesting in a few use cases. It is severely outclassed (by many orders of magnitude) by accelerator cards from AMD and NVidia.As far as I know, AMD never explained its opinion of AMX, or what AMD sales people tell clients in sales presentations.

Agree.Zen 6 architecturally is not a big step forward (relative to anyone except Intel P core). Each and every part depends on physical design and implementation to achieve competitive frequency in its target market. If it ships after July 2026, they really need to re-Zen themselves.

But in theory Zen 6 being slipping even beyond 24 months shouldn't impact its follow up. AMD is still using two teams, right?

Zen 6 architecturally is not a big step forward (relative to anyone except Intel P core). Each and every part depends on physical design and implementation to achieve competitive frequency in its target market. If it ships after July 2026, they really need to re-Zen themselves.

But in theory Zen 6 slipping even beyond 24 months shouldn't impact its follow up. AMD is still using two teams, right?

You're super eager to torture poor-poor SOC people.there is more than enough time for a refresh that is this meaningful.

forget about SoIC anywhere but extra premium client.For example, N2P compute die, and N6/N4 base die for SRAM and analog

just forget about it.RDNA3.5 + NPU -> RDNA5

would mean more GPU power, higher TOPS score out of the same or smaller die.

Well yeah, that's very very low margin stuff for people who can't ship good accelerators.And leave the CPU inference type workloads all to Intel?

The library or runtime you're using supports that too. So that's the mapping, it's already done. It was actually done first. Lisa even forced Intel to pay for it.I wonder if there is any way to remap it to the units that execute AVX-512

AMD's opinion on AMX is very clear, just buy GPUs... They even had a TCO chart to that effect...As far as I know, AMD never explained its opinion of AMX, or what AMD sales people tell clients in sales presentations.

We know functionally very little about the Zen 6 core other than it will support VP2INTERSECT, that Zen 6 is likely Family 1Ah, and that the performance increase from the 9965 to the top of SKU Venice CPU is ~1.7x...Zen 6 core doesn't seem like a super ambitious generation. Just some optimization of the cores themselves and optimizing the physical design - something AMD is good at.