DisEnchantment

Golden Member

Speculate at will

Last edited:

The sample with the date stamp is not a review sample. It's a show piece AMD is using as a prop.In your linked article, there are just 3 months between the date on the chip and the review. This time, it's more than a year.

Still very respectable.Won't go any higher, sadly. Thanks Lisa et al for blocking proper OC, garrrr.

Wouldn't showing actual review samples be embargoed anyway? There are embargoes for unboxing. Wouldn't showing the CPU itself technically count as one?The sample with the date stamp is not a review sample. It's a show piece AMD is using as a prop.

No one with actual review samples has posted photos including MFG datestamps. They're blurred.

Oh no! What will we do when they strip its metal armor and show the nude dies!Wouldn't showing the CPU itself technically count as one?

Prompt: Take the following set of things and write a poem about Zen 5's launch and performance.Zen 5 sucks worse than zen 4 but is way better than zen 4 while being both worse and better than intel while being horrible for having 15% ipc gain despite having -15% ipc gain against zen 4 despite being faster than zen 4 except when it is slower than bulldozer.

Also, benchmarks, L3 cache, rings of Saturn, chicken fingers, arm instruction set, x86/64 registers.

Oh, that must be that heat wave.16th week 2023?

Weren't the reviews 39th week 2022? Sept 26/27?

The only point was that the ES there is just three months older than the review. So this doesn't apply:The sample with the date stamp is not a review sample. It's a show piece AMD is using as a prop.

Review samples of Zen 4 were labelled with 26th week 2022. Reviews themselves happened on the 16th week of 2023 or so. This shows there usually is a notable gap.

FFS how many times do I have to run this benchmark!

When a gravitational wave flows through, Zen 5’s power shines anew.

Wait don't they get constant day time for weeks at some point of the year?On a sunny day in Siberia.

Post twice if you are having a stroke 😅Zen 5 sucks worse than zen 4 but is way better than zen 4 while being both worse and better than intel while being horrible for having 15% ipc gain despite having -15% ipc gain against zen 4 despite being faster than zen 4 except when it is slower than bulldozer.

Also, benchmarks, L3 cache, rings of Saturn, chicken fingers, arm instruction set, x86/64 registers.

Looks like they could enjoy Zen 5 more than us!Wait don't they get constant day time for weeks at some point of the year?

Oh ye cold Siberian wanderers.... rage, rage against the dying of the light!Looks like they could enjoy Zen 5 more than us!

I'll pay you if I make my "Murder in Siberia" movie and use that line in the beginning to set the tone 😛Oh ye cold Siberian wanderers.... rage, rage against the dying of the light!

Lol that would be plagiarism on my part, that's from the Dylan Thomas poem "Do Not Go Gentle Into That Good Night", as narrated by Michael Caine in the film Interstellar.I'll pay you if I make my "Murder in Siberia" movie and use that line in the beginning to set the tone 😛

Well, it can do more, I'm pretty sure. Especially if AMD didn't do whatever they do with x3d chiplets that tanks thermal conductivity so badly. I guess they cut off top part of non-x3d chiplet, weld in the cache tile and then literally glue-in the structural silicon parts on top of cores (the hottest part of the chip), hence this +20C delta between non-x3d and x3d. If they've cared a bit more they could have at least glued it in properly or didn't cut out silicon above the cores at all (but I guess that'd incur extra 0.0002c of mfg costs so sucks to be us, so to say). Even without delidding and sanding the dies proper custom loop can easily take 1.25v with non-x3d parts in linpack etc, so with x3d silicon quality we could probably have something like 5.5 ghz all-core or even more.Still very respectable.

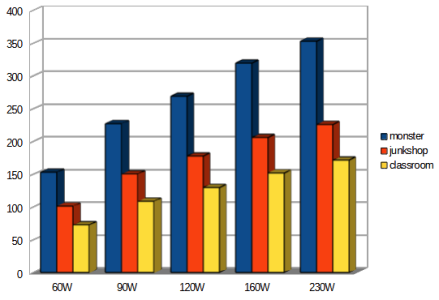

Around 22% faster than a 230W 7950X from my testing.View attachment 102874

60W: https://forums.anandtech.com/thread...ranite-ridge-ryzen-9000.2607350/post-41246800

90W: https://forums.anandtech.com/thread...ranite-ridge-ryzen-9000.2607350/post-41248191

120W: https://forums.anandtech.com/thread...ranite-ridge-ryzen-9000.2607350/post-41248591

160W: https://forums.anandtech.com/thread...ranite-ridge-ryzen-9000.2607350/post-41249476

View attachment 102875

It matches AMD Blender slide vs 7950XAround 22% faster than a 230W 7950X from my testing.

I wonder whether he reset the stats or if these surprisingly low temps are legit. If so, then it can do much more with more watts or static OC