DisEnchantment

Golden Member

Speculate at will

Last edited:

Doubt.

More likely it will be relegated to servers and Apple Mac platforms that can better benefit and profit from it.

As a desktop end-user, overall I'd agree with you since I like the idea better than having my RAM on-package so I can choose better RAM for better performance (which for me means DDR5 or in the future maybe DDR6, not LPDDR anything). But in the future if I'm forced to pick between something higher-latencly like an LPDDR product or something more DDR5/DDR6-like on-package since the "real" CPUs will be workstation/server only, I might be tempted by M1/M2/M3-like solutions. Especially if the on-package solution gets me significantly lower latency. Of course if they're sticking LPDDR on-package then I'll be screwed either way.But I still think that configurable, user replaceable LPCAMM is the way forward- 256 bits of LPDDR5X should be plenty of bandwidth for any APU that fits in a laptop thermal envelope.

She talked of Zen 5 for consumers in her first intervention just before talking of the gaming segment, that s in the first lengthy paragraph, and without providing any date.

Epyc being H2 is much later in the conference, so Zen 5 consumers products launch is not related to the date given for Epyc, that s just a wild speculation

from Paul Acorn, dunno how he managed to get to this flawed assumption.

That isn't true, in all existing AMD's APUs to this day GPU cluster is directly connected to the fabric. GPU has its own L2 and cannot utilize L3 which is part of CPU cluster. See https://chipsandcheese.com/2023/09/16/hot-chips-2023-amds-phoenix-soc/

I really hope that non-Halo Strix Point has either beefed up capacity of L2 or that AMD finally decouples L3 from CPU cluster and transforms it into a SLC from topology point of view. I believe it would also bring a benefit of reduced power consumption.

Paul Alcorn has a bias against AMD IMHO. It shows up in his "Best CPUs" articles. There are some categories that are essentialy duplicates to give Intel an extra win. Then there are stupid things like always giving Intel the win for overclocking, despite requiring the most expensive chipset and a k series CPU. Whereas for AMD you only need a B series chipset and any CPU other than the X3D ones can be overclocked.

that s just a wild speculation

from Paul Acorn, dunno how he managed to get to this flawed assumption.

Biased or not, what he wrote wasn't that Lisa Su said something. He wrote 5 hours after the earnings call, that an AMD Rep JUST confirmed that Desktop is H2. It's not that uncommon that companies give out some bits like this, when getting asked by the press.Paul Alcorn has a bias against AMD IMHO

For desktop specifically, My thought, based on all the leaks, statements, etc. is that we will get a preview in April, if anything, and a formal launch at Computex.Biased or not, what he wrote wasn't that Lisa Su said something. He wrote 5 hours after the earnings call, that an AMD Rep JUST confirmed that Desktop is H2. It's not that uncommon that companies give out some bits like this, when getting asked by the press.

I can even Leak something more: Volker Rißka of Computerbase wrote in the forum that AMD tild him at the AI Event in early December that they will launch something new at Computex.

My guess is that this was always planned to be ZEN5 DT, Computex presentation with Launch/availability in Mid/late July, 22 months after ZEN4.

Yep, he said on twitter that he was told something by somebody. As far as we know so far, it's not as if he made an interview with a transcript, let alone a vetted transcript. That is, we don't know what was literally asked nor what was literally answered, nor who the answer gave and on what authority. I admit that not quite everybody here cares for details like that.He wrote 5 hours after the earnings call, that an AMD Rep JUST confirmed that Desktop is H2.

Biased or not, what he wrote wasn't that Lisa Su said something. He wrote 5 hours after the earnings call, that an AMD Rep JUST confirmed that Desktop is H2. It's not that uncommon that companies give out some bits like this, when getting asked by the press.

I can even Leak something more: Volker Rißka of Computerbase wrote in the forum that AMD tild him at the AI Event in early December that they will launch something new at Computex.

My guess is that this was always planned to be ZEN5 DT, Computex presentation with Launch/availability in Mid/late July, 22 months after ZEN4.

Biased or not, what he wrote wasn't that Lisa Su said something. He wrote 5 hours after the earnings call, that an AMD Rep JUST confirmed that Desktop is H2. It's not that uncommon that companies give out some bits like this, when getting asked by the press.

I can even Leak something more: Volker Rißka of Computerbase wrote in the forum that AMD tild him at the AI Event in early December that they will launch something new at Computex.

My guess is that this was always planned to be ZEN5 DT, Computex presentation with Launch/availability in Mid/late July, 22 months after ZEN4.

Only Turin Dense is on 3nm though.When and if AMD moves the desktop Zen 5 to 3nm,

There's no "true" anything, just compare the chips at this point. And when comparing chips, Phoenix and Meteor are similar in efficiency.Intel has true 5nm silicon this time around with Arrow Lake.

Who the hell thinks "wish my R5 7600 was 45W instead of 65W, and I could overclock it to 65"Instead of outright performance wins, AMD could score with massive efficiency CPU's with unlocked cores and overclocking at a lower TDP.

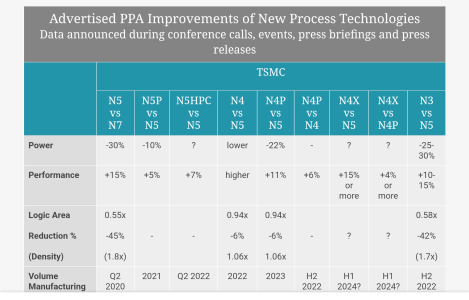

Zen 5 DT will use N4P, no?You guys need to focus more on the TSMC process that AMD uses for the desktop Zen 5 market. I am assuming that it will be N4 (4nm) which is really 5nm but significantly better efficiency and a performance uptick vs N5 silicon. When and if AMD moves the desktop Zen 5 to 3nm, will they skip the crappy N3 silicon and get the newer more enhanced 3nm TSMC coming out soon. N3 silicon is 10-15% more efficiency than the N4/4N silicon and 20%+ more efficient than the N5 silicon that Zen 4 is based on. N3 offers no performance uplift other than 10-15% better efficiency than N4 and it's much more expensive. I am not bashing TSMC, just pointing out the difficulties Apple ran into being the first 3nm customer. Apple basically cranked up the power for performance gains which offset the efficiency gains 3nm had over the 5nm TSMC silicon. They were expecting a node shrink to provide performance uplift that does not yet exist with 3nm.

Intel has already said that 18A will be 10% more efficient than 20A which is what Arrow Lake will be based on. I am looking down the road a bit and wondering where 20A efficiency land at vs. Zen 5. That is something that most people miss. Intel has true 5nm silicon this time around with Arrow Lake.

It will be very interesting later in 2024 in the CPU market as well as the GPU market simply because of TSMC silicon. People think Nvidia is such a great designer of GPU's because they use the best silicon available. I am have a personal bias in favor of energy efficiency. That's why a Zen 5 on 3nm would be interesting with either a 45W TDP or 65W TDP with 8 cores. Instead of outright performance wins, AMD could score with massive efficiency CPU's with unlocked cores and overclocking at a lower TDP.

Now that you mentioned the RDNA3 iGPU in the Exynos 2400, what is all you AMD guys take on it? The chip is now out and there are plenty of reviews and tests. The Exynos 2400 thread is open for discussion.Hans we've gone over this before. Ada isn't better because of Nvidia magically paying for better silicon. RDNA3 is a dud on N4 in Phoenix and on N5 in N31/N32 and on N6 in N33 and on Samsung 4LPP in the Exynos 2400. Four different processes and RDNA3 is a flop on all of them.

You sure? N3E has better performance/efficiency, even if it's slightly more.Moreover N3B is "crappy" but in reality it generally has better characteristics than N3E except for the cost.

We're long past the days of nodes being any decisive factor in performance and efficiency.You guys need to focus more on the TSMC process that AMD uses for the desktop Zen 5 market. I am assuming that it will be N4 (4nm) which is really 5nm but significantly better efficiency and a performance uptick vs N5 silicon. When and if AMD moves the desktop Zen 5 to 3nm, will they skip the crappy N3 silicon and get the newer more enhanced 3nm TSMC coming out soon. N3 silicon is 10-15% more efficiency than the N4/4N silicon and 20%+ more efficient than the N5 silicon that Zen 4 is based on. N3 offers no performance uplift other than 10-15% better efficiency than N4 and it's much more expensive. I am not bashing TSMC, just pointing out the difficulties Apple ran into being the first 3nm customer. Apple basically cranked up the power for performance gains which offset the efficiency gains 3nm had over the 5nm TSMC silicon. They were expecting a node shrink to provide performance uplift that does not yet exist with 3nm.

Intel has already said that 18A will be 10% more efficient than 20A which is what Arrow Lake will be based on. I am looking down the road a bit and wondering where 20A efficiency land at vs. Zen 5. That is something that most people miss. Intel has true 5nm silicon this time around with Arrow Lake.

It will be very interesting later in 2024 in the CPU market as well as the GPU market simply because of TSMC silicon. People think Nvidia is such a great designer of GPU's because they use the best silicon available. I am have a personal bias in favor of energy efficiency. That's why a Zen 5 on 3nm would be interesting with either a 45W TDP or 65W TDP with 8 cores. Instead of outright performance wins, AMD could score with massive efficiency CPU's with unlocked cores and overclocking at a lower TDP.

PPW worse. Density better. For Zen 5 dense it could be a good match but the cost never works out. It is not "crappy", it's too costly for what it does.Aaaaeeeh. You sure? N3E has better performance/efficiency, even if it's slightly more.

Yeah, N3B's density is better than N3E due to multi-patterning. N3E is cheaper to implement due to single patterning but the density is lower than N3B process.PPW worse. Density better. For Zen 5 dense it could be a good match but the cost never works out. It is not "crappy", it's too costly for what it does.

Also @Hans Gruber, consider that TSMC says N3E is about 18% more performance than N5 and N4P is also about 15% performance than N5. Is that extra 2.6% really what will make or break Zen 5?

PPW worse. Density better. For Zen 5 dense it could be a good match but the cost never works out. It is not "crappy", it's too costly for what it does.

Also @Hans Gruber, consider that TSMC says N3E is about 18% more performance than N5 and N4P is also about 15% more performance than N5. Is that extra 2.6% really what will make or break Zen 5?

I think it's fair to say the N3 silicon will be used with the Turin server chips and N4 will be used for the desktop CPU's. Down the road that may change in 2025.Zen 5 DT will use N4P, no?

Well, he writes for Tom's, what did you expect ?Paul Alcorn has a bias against AMD IMHO. It shows up in his "Best CPUs" articles. There are some categories that are essentialy duplicates to give Intel an extra win. Then there are stupid things like always giving Intel the win for overclocking, despite requiring the most expensive chipset and a k series CPU. Whereas for AMD you only need a B series chipset and any CPU other than the X3D ones can be overclocked.

Does anyone know what the shortest time has been so far between AMD officially announcing the next gen Zen CPU release date for DT, until actual availability?

I'm trying to estimate the expected availability date of Zen5, based on what date we are at now. E.g. if the shortest time is 3 months, if they would announce it today, it would mean availability is beginning of May based on past track record.

Wow, much shorter than expected.I don't know for all of them, but for Zen 3 and Zen 4 it was 1 month from announcement to launch.

How did ”we” know that for certain?We knew what was happening for certain, but I can't remember if that was mainly because of the calendar, Z4 certainly lined up with 24 months after Z3.