DisEnchantment

Golden Member

Speculate at will

Last edited:

I wasn't asking about regulators per seThey already have built in regulators per core since Zen 1, what Intel will implement as DLVR.

I wasn't asking about regulators per se

Have you heard of any plans to design FIVR-based PDN for Zen6?

Once more, I wasn't asking about specific regulator, but about the likely design and implementation of PDN in general, or was I unclear?Then you re asking about something whose significance is unknown for you..

Oh... I appreciate your knowledge but please don't bother yourself anymore (lest you be embarassed)Do you know what is FIVR..?..

Fully Integrated Voltage Regulator.

So not even Forksheet nodes?N5 was the last major one for speed until like the CFET era.

Those are just to keep the semblance of power/perf scaling going, just like nanosheet GAAs.So not even Forksheet nodes?

Have you heard of any plans to design FIVR-based PDN for Zen6?

Once more, I wasn't asking about specific regulator, but about the possible design and implementation of PDN in general, or was I unclear?

Oh... I appreciate your knowledge but please don't bother yourself anymore.

rivatuner guy? your response reads like himOh... I appreciate your knowledge but please don't bother yourself anymore (lest you be embarassed)

This comparison should flatter me up? )rivatuner guy? your response reads like him

only if you lock it to 250w in the bios. otherwise it will go higher and higher. intel all alone could advertise their cpus as eco friendly heating units in comparison with burning natural gas for heat in winter.I my talking of real TDP, not of the fake TDP advertised by Intel, the 13900K is advertised as 125W but we all know that it stick to 250W when loaded by whatever multithreaded load.

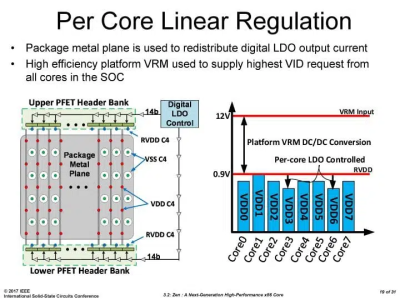

Zen 1 has LDO not IVR. Purpose is same, just different characteristicsThey already have built in regulators per core since Zen 1, what Intel will implement as DLVR.

Zen 1 has LDO not IVR. Purpose is same, just different characteristics

I calculate for TDP not something else so why pulling something that has a complete different definition to begin with?I my talking of real TDP, not of the fake TDP advertised by Intel, the 13900K is advertised as 125W but we all know that it stick to 250W when loaded by whatever multithreaded load.

You stated a 51000 Cinebench score for ARL that is roughly 35% higher than the 13900K, Igors lab say that it s someething like 10-15% in MT, so you stated 2.3-3.5x the leaked improvement.

Since you said 48000 for Zen 5 it s obvious that you are feeding yourself with hopes that it well perform lower than ARL 8 + 16, unfortunately for you that wont be the case.

Possibly that they added a 2 x 256b unit, otherwise what would be the use to increase L1 size by 25%..?

This would allow to execute either a second 512b instruction, or 2 x 256b/128b/64b instructions, not economical to use a 256b unit to process a 64b instruction, but since it s there it s better than to add a separate 64b unit.

I calculate for TDP not something else so why pulling something that has a complete different definition to begin with?

Besides that's what Intel is selling and tiering the SKU's. So why would I have to go with something that is lottery random instead of matching what they will be selling it for?

I did say "in theory" and I also did say it was based on leakers (MLID) so blame them for the inaccuracy.

Besides this was before Intel started axing designs and pulling follow-on designs up ahead of schedule as replacement and before Intel ditched the very design I theorized there for one without hyperthreading.

Eh? What do calculations have to do with hopes? It's the calculation that tell the situation in the first place, hence, my conclusion based on that. You got things backward here.

That said Intel's axing actions already proofed those original designs weren't up to the task to beat Zen5. Silently replacing the engine and claiming it was originally better? Is that it now?

AMD s LDO use a switching mode supply

Zeppelin is the first design in which AMD has extensively utilized integrated voltage regulators. Unlike the fully integrated voltage regulator (FIVR) used in Haswell and Broadwell CPUs, AMD's regulator implementation isn't based on ultra-high speed switching circuitry. The integrated voltage regulators in Zeppelin are ultra-high efficiency digital low-dropout (dLDO) type of regulators. Most of the different domains (cores, caches, data fabric, etc.) have their own dLDOs and they can all be controlled individually.

View attachment 84229

Linear regulation not switching. Not sure about your source of AMD's LDO being switching regulators.

Also Stilt has described them here https://forums.anandtech.com/threads/ryzen-strictly-technical.2500572/

Lol ... somehow he managed to throw three different types of VR together and put it in one Zen package 🙂Linear regulation not switching. Not sure about your source of AMD's LDO being switching regulators.

"...AMD s 1) LDO use a 2) switching mode supply for each core..."

...

...

"...the two first chapters are enough to understand how AMD s LDO work:

3) Switched Capacitor wikipedia

Sorry, but I have to admit, you areEdit : To end the debate you have the explanations at the begenning of this article, the two first chapters are enough to understand how AMD s LDO work

It looks encouraging that samples of these are out already.Videocardz.com

Some Strix Point data. A lot of It looks inaccurate.

@Abwx That's why I wrote a lot of the data looks incorrect.

Yea, server ones have been out for a while.It looks encouraging that samples of these are out already.

Yea went better than expected and stuff got pulled in.It looks like AMD may compress this time with Zen 5 generation.

We gonna have Zen5X3D on shelves in March 2024?Yea went better than expected and stuff got pulled in.

No. Desktop doesn't matter. Shelves don't matter.We gonna have Zen5X3D on shelves in March 2024?