- Mar 3, 2017

- 1,779

- 6,798

- 136

Maybe they really are waiting for the 14900K fix so they truly can obliterate them in launch benchmarks.AMD said there was issues and he doesn't believe AMD so obviously theres no issues and the delay is because AMD felt like it.

There probably IS an issue but not the one that AMD is telling us.AMD said there was issues and he doesn't believe AMD so obviously theres no issues and the delay is because AMD felt like it.

YES.Maybe they really are waiting for the 14900K fix so they truly can obliterate them in launch benchmarks.

Ian said that Zen 5c would see a much smaller drop in frequencies compared to what Z4c had relative to the classic cores.

Interesting.

No. AMD said this during the post-tech-day briefing in the context of Strix Point's N4P Zen 5 cores and N4P Zen 5c core sizes, the latter being just 25% smaller than the former. (Whereas the difference was 35% between Phoenix 2's Zen 4 and Zen 4c cores.) These lowered space savings are because AMD had to work within stricter constraints WRT Voltages and clocks in order to make the compact cores work as a support to the classic cores the way as AMD wanted them.Well, this expected if they talk about Epyc : 4nm vs 3 nm

Okay... AMD are lying publicly when they say that they had a QA issue with the first batch. From this follows that they are either going on lying publicly by saying that they are recalling the first batch from their channel partners, or it follows that they are happy to sink the cost of the product recall just for the nicer comparison in reviews.BINGO!

Now that's a logically possible motive behind AMD's decision.

Nah. If that is the case they wouldn't have to reexamine the entire current inventory.YES.

BINGO!

Now that's a logically possible motive behind AMD's decision. The greater the average performance percentage difference, the better Zen 5 looks to the public!

AMD should've just said so.

"We regret to inform you that we don't feel this is the right time to publish Zen 5 benchmarks. We will wait for our dear competitor to get their act together before we thoroughly embarrass them".

OK, you are telling me that they will get the CPUs back, every single one of them, run them through their QA test gauntlet and get them back on shelves ON August 8th for the single CCD CPUs????Nah. If that is the case they wouldn't have to reexamine the entire current inventory.

...only a part of the inventory which was first to arrive at distributors.If that is the case they wouldn't have to reexamine the entire current inventory.

Does this mean that Turin-dense is going to be early, or that Turin-classic is going to be late?Mike Clark said:And we're going to deliver 3nm here in short order with 4nm; basically, they're on top of each other.

If it comes to that, they will sell it in bulk to Chinese businesses and then you bet you will find them on Ali Express.(Besides, they might just discard it rather than refurbish it.)

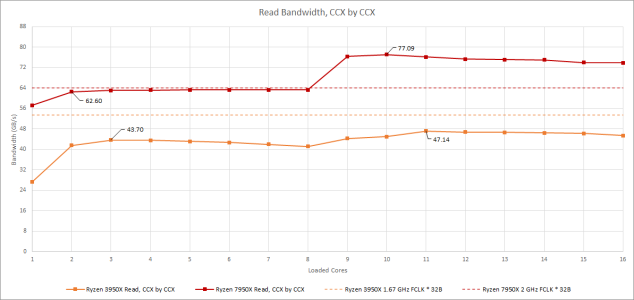

Yeah, by a lot, each CCD gets 2*32B fabric uplink (aka the new norm going forward).

That's not the limiting factor at all.

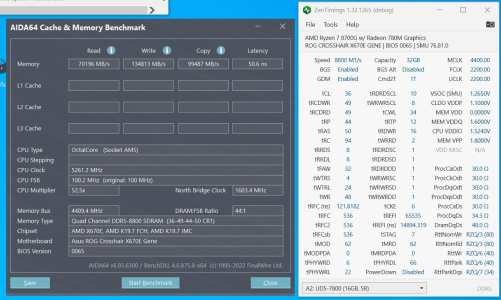

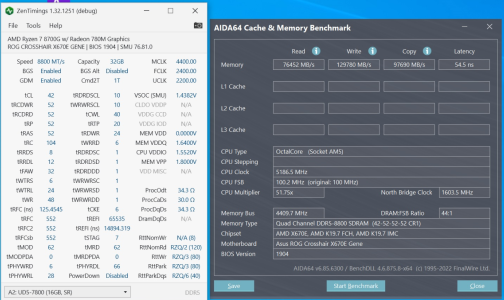

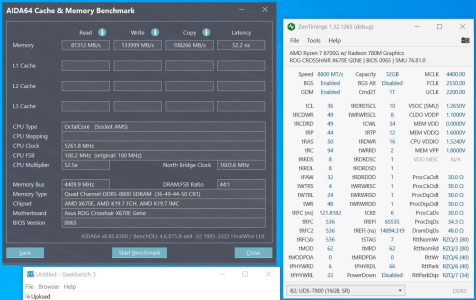

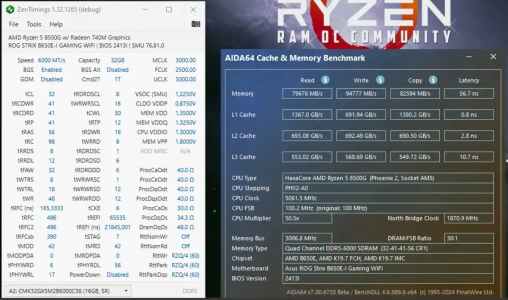

And I believe DDR5 @ 8000 MHz dual channel would be ~ 128 GB/s ? So over twice the membwLPDDR5x @ 8533 MHz with 256-bit interface is 273 GB/s.

And I believe DDR5 @ 8000 MHz dual channel would be ~ 128 GB/s ? So over twice the membw

I don't understand the significance of the 2*32B fabric uplink thing if anyone cares to expand on that. I can't imagine that would bottleneck DRAM bandwidth right? But I'm guessing improves inter-CCD communication?

Still below Intel's CPU killing voltage.The hysteria is being overclocked to the max here with voltage set to red.

The CPUs sold in a few weeks will not be the same ones that are being recalled lol. The delay is likely just the time needed to ship out and restock shelves with chips that have been fully validated.OK, you are telling me that they will get the CPUs back, every single one of them, run them through their QA test gauntlet and get them back on shelves ON August 8th for the single CCD CPUs????

Please, please THINK about that for a second.

Doing that FOR all shipped CPUs regardless of region or territory means they have testing facilities in every region within reach. Please tell me that you don't believe that to be true because that would be ABSURD. Even Intel doesn't have that.

Possible I guess. Still, it would have been better if AMD had disclosed the exact nature of the issue and how an improperly validated CPU was gonna behave because quite a few people out there may have paid full or even more than full price for their CPUs that weren't supposed to be on sale yet and they will live with them and encounter some weird issue and think AMD sucks and the retailer isn't gonna bother about calling the customer to get that CPU back because they already got what they wanted: the customer's cold hard cash!The delay is likely just the time needed to ship out and restock shelves with chips that have been fully validated.

Possible I guess. Still, it would have been better if AMD had disclosed the exact nature of the issue and how an improperly validated CPU was gonna behave because quite a few people out there may have paid full or even more than full price for their CPUs that weren't supposed to be on sale yet and they will live with them and encounter some weird issue and think AMD sucks and the retailer isn't gonna bother about calling the customer to get that CPU back because they already got what they wanted: the customer's cold hard cash!

I hear you.If it's due to not having run all the validation checks as the statement by AMD's spokesperson says, AMD wouldn't know with reasonable certainty (99.999%+) how the CPU would behave - and that's the point of recalling it!

First N3E part in GA is M4, that is the opposite of a server part.N3E is enterprise/server, N3 is efficient junk. N3P is the value play performance/efficiency mainstream 3nm. N3X is for Nvidia, high end performance and increased silicon density.

Ah, so you are green with envy after all.Is AMD paying you for your statement? Or are you an AMD voluntary public service agent here on the forum?

https://wccftech.com/chinese-shopke...5-desktop-cpu-prices-lower-ryzen-7000-series/According to the retailer, the AMD Ryzen 9 9950X 16-Core CPU would cost $499 US (3631 RMB), the Ryzen 9 9900X 12-Core CPU would cost $399 US (2904 RMB), the Ryzen 7 9700X 8-Core would cost $299 US (2176 RMB) while the Ryzen 5 9600X 6-Core CPU would cost $229 US (1666 RMB).

No.N3E is enterprise/server

No, N3b is an entirely different node altogether.N3 is efficient junk

No.N3P is the value play performance/efficiency mainstream

That's an overdrive node strictly for AMD usage more or less.N3X is for Nvidia

If they can release it to compete head-to-head against Intel's next gen for the gaming crown, I don't know why they would artificially delay to CES and potentially give Intel a few months of the gaming crown (pending how the new processors actually perform, of course).is the zen 5 X3D still launching in September?

I kinda doubt it now. Probably CES 2025.