- Mar 3, 2017

- 1,779

- 6,798

- 136

I don't think there will be a net loss in efficiency?From TSMC official numbers (best case scenarios)

N4P --> N3E is ~10% efficiency gain.

N5 --> N4P is ~22% efficiency gain

N5 --> N3E is ~35% efficiency gain

Even 15% efficiency gain from process is significant, if AMD cannot extract that much at the very least then it is poor execution.

From architecture they should be able to extract some efficiency as well.

But if net loss of efficiency due to bigger/wider cores then the execution is lacking.

They might be driving the core to even more frequencies is the only reason that would be acceptable.

IMO the only way forward is a significantly wider core, which absolutely means more power, when totally maxed out (far past it's efficiency optimum).I do not see a world in which peak power for Zen 5 per core is lower than that for Zen 4.

Maybe if it had a good node shrink to prop it up, but N4P v s N5 ain't it. With that in mind, I'm not sure backtracking on power limits would make sense.

Lol, everytime I see the Dense core variant mentioned.....Zen5 to use CCX design? What's the purpose? Maybe a typo(Zen5c instead of Zen5)?

View attachment 82572

Yeah this is a straightforward consequence of a wider, deeper microarchitecture which AMD somewhat explicitly alluded to especially on the frontend and I believe will take Zen to parity with Golden Cove on sheer size. All else equal - and the node isn't changing afaict for mobile - it's going to require more at a given frequency unless gating was just lackluster on Zen 4. Of course for a similar performance itself I suspect energy efficiency or power efficiency will be improved, likely because you won't have to clock as high/raise voltages as high. Idle could improve as well but that's more uncore stuff.I don't think there will be a net loss in efficiency?

I specifically stated higher peak power. I'm going to double down on this actually. I think that at any given clock frequency Zen 5 will require more power than Zen 4.

That doesn't mean I believe Zen 5 will sport worse power efficiency than Zen 4 (at least at any frequency where it actually matters). Just that the peak of what is possible will be increased.

What, from the tweet, makes you draw this conclusion?Zen 5 hasn't powered on yet?

If it will have 16 CCDs, then that seems to imply that the IO die has an extra cpu link that is not currently being used? I wonder if they could build an 8 chiplet device with dual links per chiplet.Zen5 to use CCX design? What's the purpose? Maybe a typo(Zen5c instead of Zen5)?

View attachment 82572

Power on usually happens after getting A0 silicon back from the fab doesn't it? If A0 is just out, I'm assuming power on is going to happen at a later date.What, from the tweet, makes you draw this conclusion?

I haven't watched the talk in question, but apparently Papermaster said at the Oracle Exadata server platform launch that Zen 5 samples are running in the lab already.Power on usually happens after getting A0 silicon back from the fab doesn't it? If A0 is just out, I'm assuming power on is going to happen at a later date.

Also for a 1H 2024 launch, I thought they should be on early ES already.

Yep, and it is quite likely that they will, for low core count / high bandwidth needs. They did the same for Genoa already with their 4 CCD SKUs.If it will have 16 CCDs, then that seems to imply that the IO die has an extra cpu link that is not currently being used? I wonder if they could build an 8 chiplet device with dual links per chiplet.

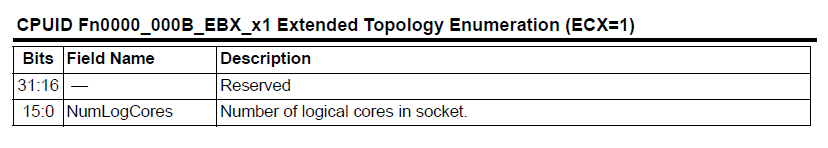

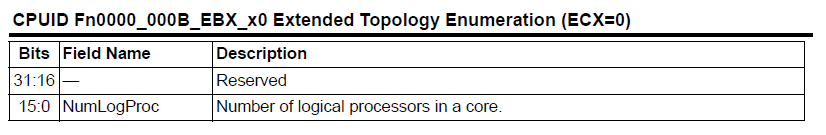

Is this a clue for future SMT4?And thread per cores also, in same register by changing InputEcx.

Engineering samples and early work to verify it for server use I'd imagine.whatever that means

Other way around most likely.Is this a clue for future SMT4?

Man you're gonna give wrong ideas to people like that.Other way around most likely.

4 cores working together to boost a single thread?Other way around most likely.

Lack of SMT in the future.4 cores working together to boost a single thread?

Such a silly idea, but I thought of speculative execution on steroids - instead of guessing the branch and executing it, just split it in 2 and give to 2 cores. then 4, than 8 cores. If a core gets something wrong, flush the whole core 😂4 cores working together to boost a single thread?

Well, nope.Likely SX

AMD always does their own thing that in no way is related to Intel.then that means Zen 5 won't have it either!

I said SX not STX.OK so if Arrow Lake won't have SMT then that means Zen 5 won't have it either!

I like it!Such a silly idea, but I thought of speculative execution on steroids - instead of guessing the branch and executing it, just split it in 2 and give to 2 cores. then 4, than 8 cores. If a core gets something wrong, flush the whole core 😂