- Mar 3, 2017

- 1,779

- 6,798

- 136

Zen3 wasn't doing the bulkiest, most overkill AVX-512 implementation known to man.Not Zen 3 levels of improvement

lmfaoooApparently I woke up on the darkest timeline side of the bed today since I've learned that MLID was apparently correct.

Tech bros, I'm not feeling so well right now.

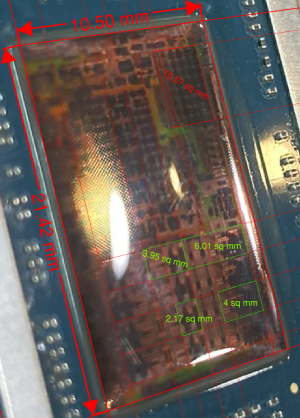

Lol, getting within 1mm2 is probably purely luck on my part since it depended on which pixel I measured from.

Fwiw, TSMC N4P comes with a 6% reduction in area for logic in comparison to TSMC N5, but 16% higher IPC with a 26% larger core and presumably 34% more transistors (1.25*1.06 = 1.34) is right on the money with respect to the square law of scaling (square roof of 1.34 = 1.15). Not Zen 3 levels of improvement (19% higher IPC, 200 MHz higher max clocks, for 8% larger CCD) but at least Zen 5 isn't under par. I'm hoping that the 16% IPC uplift is true for general performance and not significantly skewed due to AVX512.

Zen3 wasn't doing the bulkiest, most overkill AVX-512 implementation known to man.

The bulk of area growth for Z5 is it.

Not sure how useful it is for consumers outside of PS3 emulation but for the HPC market? Could be good.We will see how good this bet by AMD on AVX-512 will turn out in the long run. AMD had a good enough implementation in Zen 4 and they doubled down on it.

Not very, Intel doesn't support the ISA in client.Not sure how useful it is for consumers outside of PS3 emulation but for the HPC market? Could be good.

We will see how good this bet by AMD on AVX-512 will turn out in the long run. AMD had a good enough implementation in Zen 4 and they doubled down on it.

It's literally AVX-512 lowered to 256b native vectors.AVX-10 is more future proof for upcoming massive parallel designs.

Not sure how useful it is for consumers outside of PS3 emulation but for the HPC market?

Eh?It's literally AVX-512 lowered to 256b native vectors.

No.I thought the point was an SVE like 'write once run everywhere'

no, you compile to either 256b or 512b target.or 512 bit units on the P cores?

More people talking about AMD = better, I don't think they could care less about whatever happens in the internet rumor mill.Either AMD marketing team is a bunch of incompetent fools, or AMD as a whole is a bunch of incompetent fools.

Qualcomm, MediaTek/Nvidia and AMD have told their plans to Microsoft. They are picking their priorities with a lot more information than we have.I have to say. Looking at where x86 chips are going, I am actually not surprised one bit that Microsoft is showing middle finger and pushing for WoA initiative even harder.

AI obviously.

L3 portion looks like it shrunk 1.5 nodes rather than 0.5.

Maybe the TSVs were moved from there?

CES'25.

I am going to guess that it has to do with volume, progress and debugging. For example, aside from the AIO, which is different between desktop and server, thr Zen 5 cores are identical except binning IMO. So basically one chiplet and 2 AIO's and a lot of products can come out. Zen 5C is only a small change from Zen 5 core (Identical except cache/speed), and you have 2 complete product lines. And a lot of $$$. The others require a lot more tuning/development/testing.halo and fire range on january 2025??????? why so late

Because Strix Point was pulled ahead to meet MS Copilot + PC push. CES 2025 was the original revised intended target.halo and fire range on january 2025??????? why so late

No?CES 2025 was the original revised intended target.

When it was? It was supposed to be a early 2024 thing before "plans changed", no?