there you go

AMD Eng Sample: 100-000000114-07_22/15_N

AMD Eng Sample: 100-000000114-07_22/15_N

But K8 and K10 was still K7 based which was decade old microarchitecture. There was such a limiting things like ALU-AGU clusters. Intel's Core1 Yonah had modern decoupled ALUs and AGUs allowing to extract much higher IPC from code. Bulldozer had also this modern decoupled design (2xALU + 2xAGU), much wider OoO window and yet often much lower IPC than old K8/K10 (3x ALU-AGU).Bulldozer's core(K10) of 2 ALUs and 2 AGUs were more efficient than Greyhound's core(K8) of 3 ALU or 3 AGU. The entire Bulldozer architecture in itself has 4 ALUs, 4 AGUs, 4 FPUs. So, it isn't really surprising for a smaller core on a more advanced node to be able to have four ALUs and four FPUs. Since, Bulldozer already had four ALUs and four FPUs on 32nm => It isn't a far push to get Zen on 14nm to also have four ALUs and four FPUs in less area.

The only case of AMD increasing ALU counts is from the total accessible in a CMT module. As the CMT architecture can be re-assembled into a SMT architecture with ease.

Apple's using core with 6xALU since 2017

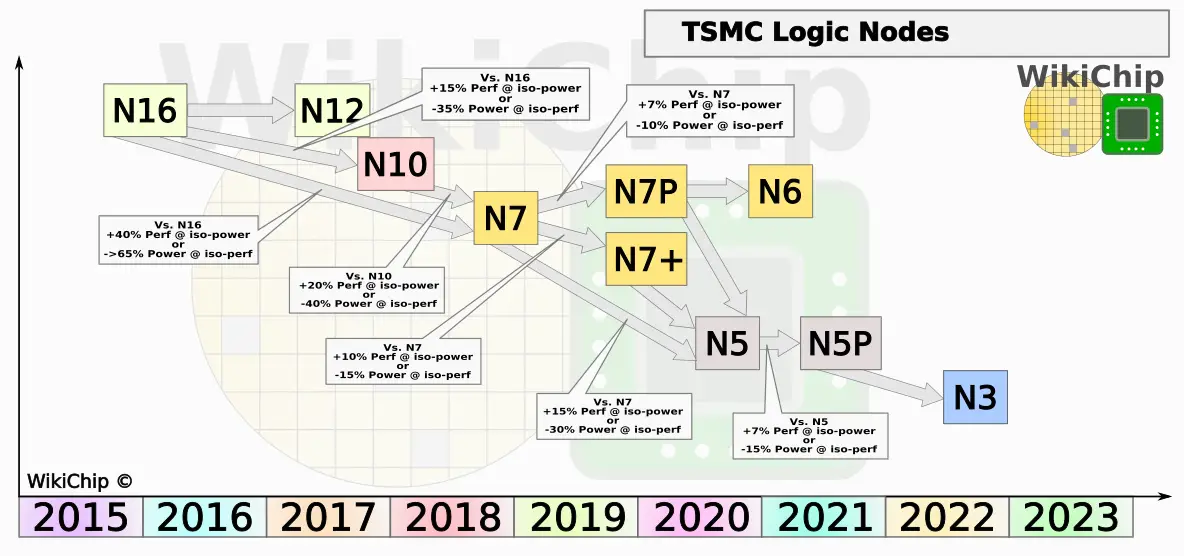

N7+ is better but neither of them are much better than N7 in my opinion, it wont change much if it's N7P or N7+, even N6. N5 would be exciting, though.

Preventing leaks for a new chip typically means either:Every single person in the rumour scene has been saying the same thing for a while. Getting any info from AMD is very difficult now. AMD are going to very great lengths to prevent any sorts of leaks.

Their prime motivator 100% is demand drop. They're literally about to launch a ryzen 3000 refresh and potentially soon zen 2 apus. Ryzen 3000 sales are still incredibly strong for AMD right now, what better way to absolutely destroy their sales than to announce that zen 3 is only a few months away and it probably destroys zen 2 in performance.Preventing leaks for a new chip typically means either:

A (Demand-drop) I don't see as an issue for AMD. They can easily use the capacity for mobile chips, etc.

- A: Preventing a demand-drop for the current generation from customers realizing they are buying soon outdated products.

- B: Preventing the competition from using that information to react to the new products early.

B (keep Intel in the dark) Is much more likely. AMD has successfully fooled Nvidia with Navi pricing. This time it may be Intel ...?

Which is newer/better/more exciting? Were we hoping for one vs the other? 🙂

Zen + was basically Zen redux. Zen 3 is a new design so they'll use the full advantages of the node.i'm looking forward to see if that holds true with zen 3 CCDs. technically 12LP was 10% denser yet zen+ SKUs have the same area than its zen 14LPP counterparts.

maybe it did shrink, but just CCX, cache and other parts except the I/O did, but it's not really noticeable.

I haven't been following this at all, but what would be a reasonable expectation for performance? Will Intel have to give up the gaming crown? I'm stuck at nearly 2 yr old 9900K @ 5GHz and haven't used AMD since A64, will or should the new lineup be able to kick Intel down from the specific best case they have at the moment? If I can get 10 or 12 cores and indisputable better performance in the best Intel case (gaming) then I may actually consider Zen 3 whereas I earlier had resigned to not be able to get a worthwhile upgrade for 1-2 more years. Or is Zen 3 targeting something completely different?

Maybe. That depends on their goal. Not maximizing transistor density may be one way of enabling higher clocks without being thermally limited.Zen + was basically Zen redux. Zen 3 is a new design so they'll use the full advantages of the node.

Nobody knows. Each generation naturally targets better performance but only independent reviews of the final product can show its strong and weak sides.I haven't been following this at all, but what would be a reasonable expectation for performance? Will Intel have to give up the gaming crown? I'm stuck at nearly 2 yr old 9900K @ 5GHz and haven't used AMD since A64, will or should the new lineup be able to kick Intel down from the specific best case they have at the moment? If I can get 10 or 12 cores and indisputable better performance in the best Intel case (gaming) then I may actually consider Zen 3 whereas I earlier had resigned to not be able to get a worthwhile upgrade for 1-2 more years. Or is Zen 3 targeting something completely different?

Aside from benchmarks it's unlikely you would see any difference while playing on or using your computer. Just go crazy on the GPU and enjoy. 😉I haven't been following this at all, but what would be a reasonable expectation for performance? Will Intel have to give up the gaming crown? I'm stuck at nearly 2 yr old 9900K @ 5GHz and haven't used AMD since A64, will or should the new lineup be able to kick Intel down from the specific best case they have at the moment? If I can get 10 or 12 cores and indisputable better performance in the best Intel case (gaming) then I may actually consider Zen 3 whereas I earlier had resigned to not be able to get a worthwhile upgrade for 1-2 more years. Or is Zen 3 targeting something completely different?

Didn't exactly say that they would, although I now see that it could be seen as such.Maybe. That depends on their goal. Not maximizing transistor density may be one way of enabling higher clocks without being thermally limited.

We don't know enough details but I'd be incredibly surprised if they packed 100% of the transistors per mm2 onto the chiplets.

How else would they fit in 12 ALUs so they can stop being lazy stupid x86 engineers?Maybe. That depends on their goal. Not maximizing transistor density may be one way of enabling higher clocks without being thermally limited.

We don't know enough details but I'd be incredibly surprised if they packed 100% of the transistors per mm2 onto the chiplets.

If 12 is good, surely 24 is betterHow else would they fit in 12 ALUs so they can stop being lazy stupid x86 engineers?