It’s not just a library thing afaict, you have connector/domino logic or other physical design stuff that inflates area. That and the literal layout of the internal blocks changes the higher speeds you need.Hypothetical Question

Let's take 2 CPUs. They both use the identical core architecture/caches. Overall multicore performance is also identical (4.4×10=44, 4.0×11=44).

(A) 10 cores @4.4 GHz using HP library

(B) 11 cores @4.0 GHz using HD library

Which solution is better in terms of PPA? I am curious which will take up more die area and which will be more efficient at multicore performance.

I don’t think btw that even AMD uses HP libraries for their mobile CPU’s even on Zen 4. If you read, they used HD libraries with Zen 2 and probably Zen 3 but relaxed track heights. Basically N7 was hitting 4GHz+ on HD cells with some relaxed stuff.

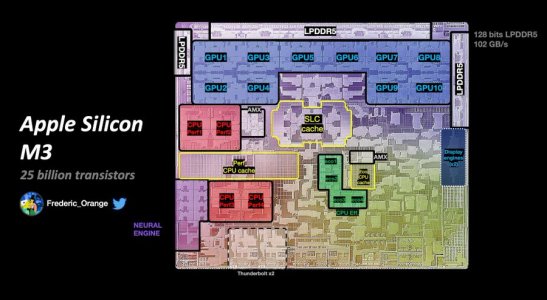

Whatever they did or do I will assure you it won’t be that bloated relative to AMD or Intel’s big designs. It will be big of course but that’s because the architecture will be big.