-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

New Zen microarchitecture details

Page 57 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

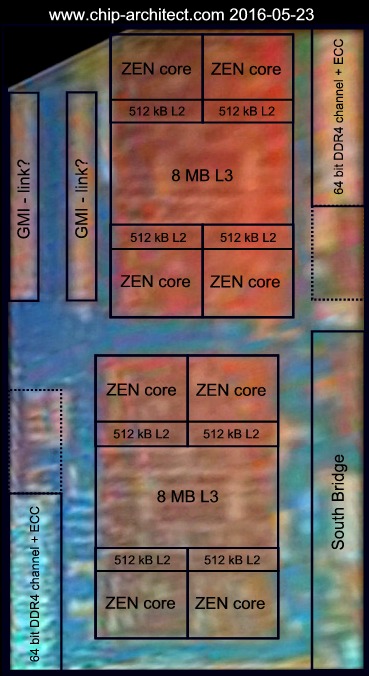

"GMI Link" wouldn't these be Pci-e link's on this?

Also I don't believe there's any Southbridge functionality on Summit ridge, only Bristol. - i would suspect 'remaining' NB logic instead.

The Stilt

Golden Member

If Bristol Ridge is a SoC (FCH on die), doesn't it mean Summit Ridge (Zeppelin) has to be as well :sneaky: Well not necessarily since the FCH on Bristol Ridge can be disabled, but... :sneaky:

GMI is used for inter-die communication, both within and outside the same package. Basically it is HT / LDT on Sustanon 😀

GMI is used for inter-die communication, both within and outside the same package. Basically it is HT / LDT on Sustanon 😀

I was under the impression Summit didn't have FCH on die, and would require full functionality of the external Promontory FCH.

with BR I was also under the impression its FCH would only be partially utilized. (it's disabled completely on FM2??)

There was an old block diagram getting around which I based these assumptions off, but not sure if there's anything more recent (?)

as for GMI, well for internal fabric yeah, but I didn't think there'y be any external interface on these die's

with BR I was also under the impression its FCH would only be partially utilized. (it's disabled completely on FM2??)

There was an old block diagram getting around which I based these assumptions off, but not sure if there's anything more recent (?)

as for GMI, well for internal fabric yeah, but I didn't think there'y be any external interface on these die's

The Stilt

Golden Member

I don't think GMI will be included in Raven Ridge. HT links existed in Bulldozer based CPUs, but weren't implemented in Bulldozer based APUs.

GMI is just used to communicate between the CPU dies on the same or on a different package, same as HT.

If it is possible to replace another Zeppelin die with a GPU ASIC, I have no idea. At least there wouldn't be any advantages I could think of. The PCI-E bandwidth has never been the limiting factor for APUs and having GMI links on die will consume additional (expensive) die area.

GMI is just used to communicate between the CPU dies on the same or on a different package, same as HT.

If it is possible to replace another Zeppelin die with a GPU ASIC, I have no idea. At least there wouldn't be any advantages I could think of. The PCI-E bandwidth has never been the limiting factor for APUs and having GMI links on die will consume additional (expensive) die area.

I need to get the basic confirmed here. I am looking at a 8c native cpu. Not interposer. Right?

As amd is severily ressource starwed that probably means /confirms thats the only variant at launch and that the rest is defects/cuts?

Secondly compared to orochi as i recall that cpu had more space wasted on non cpu core logic and cache?

As amd is severily ressource starwed that probably means /confirms thats the only variant at launch and that the rest is defects/cuts?

Secondly compared to orochi as i recall that cpu had more space wasted on non cpu core logic and cache?

The Stilt

Golden Member

If each core (in a 4 core cluster) only has access to one memory controller then doesnt that cripple single thread performance?

Obviously both CCXs connect to the same northbridge, which is located before the memory controllers.

Ok... wondering if AMD makes the Conroe Miracle and delivers a brutal ammount of improvement. A miracle like that could start a revival on the PC market.

Except it wasn't really a miracle. Between Pentium 3 and Conroe were Banias, Dothan, and Yonah (ie Pentium M and Core), so there was some guidance as to Conroe's performance. Only if you were living under a rock and only knew about Pentium 4 would it seem like a miracle.

If each core (in a 4 core cluster) only has access to one memory controller then doesnt that cripple single thread performance?

I don't believe my HW-E can use more than a single memory controller with a single thread either. I tested memory bandwidth with Sissoft Sandra and there's a huge difference in ST and MT mode.

itsmydamnation

Diamond Member

shameless stolen from SA:

http://seekingalpha.com/article/397...al-technology-media-telecom-conference?page=5

also on the GMI and NB, my guess is that one computer unit has 4Core, 8mb L3, one DDR4 interface and one north bridge, whats the point of "distributed memory controllers" if the thing that connects to it isn't. In the die shot the two units are a mirror of each other, this would help with cross connecting two internal north bridges. The next set of questions would be how/ where are the GMI links connected and links to south bridge, one to each north bridge? gmi on one south on the other etc.

the 32 core chip would then look like some form of a 4 or 8 stop ring bus.

http://seekingalpha.com/article/397...al-technology-media-telecom-conference?page=5

Mark Papermaster said:Absolutely. So what we did with Zen, it is truly a ground up new design. It leverage the deep experience we had in 64-bit x86, which of course, AMD was the pioneer in the industry with this technology. But when I say from scratch design, I mean really retooling how you get performance and actually very high performance.

And so we went about it with really three facets. You have to basically modify the execution engines to tune them up. We tune them up in a way to basically improve the efficiency of the processing. We've tuned up how you cache, right, so how instructions can install, if you don't have the right the local cache instructors, so we tuned up our cache sub-system.

And then you have to feed those engines and so we tuned up our IO and memory. And so this was just roll up the sleeves, hard-nosed microprocessor engineering to get that kind of bump, where you have 40% instruction per clock versus our current generation, which is shipping in Bristol Ridge. That's huge and it's a result of that hard-nosed engineering.

also on the GMI and NB, my guess is that one computer unit has 4Core, 8mb L3, one DDR4 interface and one north bridge, whats the point of "distributed memory controllers" if the thing that connects to it isn't. In the die shot the two units are a mirror of each other, this would help with cross connecting two internal north bridges. The next set of questions would be how/ where are the GMI links connected and links to south bridge, one to each north bridge? gmi on one south on the other etc.

the 32 core chip would then look like some form of a 4 or 8 stop ring bus.

Last edited:

AtenRa

Lifer

Well lets see if ZEN will be available to retail by the end of the year.

Harlan Sur

So should we anticipate something like desktop end of this year, server first half of next year and then client compute mainstream as we roll through the remainder of 2017? Is that kind of how we think about it?

Mark Papermaster

Well, the order is correct. We haven't release these specific times. But again, we're on track, what we said is we'll be sampling to priority customers at the end of this quarter, on track there. We said first full year of our production ship next year right on track, and again, in that order of desktop, server and the client compute.

Dresdenboy

Golden Member

Let me emphasize the base for the 40% IPC increase here:

Some schematic showing the CCX:

Mark Papermaster said:And so this was just roll up the sleeves, hard-nosed microprocessor engineering to get that kind of bump, where you have 40% instruction per clock versus our current generation, which is shipping in Bristol Ridge.

Some schematic showing the CCX:

Patent said:In some embodiments, all or a portion of the compute units 104-0 through 104-N are processor cores (e.g., central processing unit (CPU) cores).

Last edited:

Found an EE Times article about a new collaborative effort for a cache-coherent interconnect for accelerators which AMD is involved in amongst others.

Not sure this is directly relevant to Zen, but it may well end up attached to a future server chip from AMD which has a Zen successor on it.

Link

Not sure this is directly relevant to Zen, but it may well end up attached to a future server chip from AMD which has a Zen successor on it.

Link

nismotigerwvu

Golden Member

Except it wasn't really a miracle. Between Pentium 3 and Conroe were Banias, Dothan, and Yonah (ie Pentium M and Core), so there was some guidance as to Conroe's performance. Only if you were living under a rock and only knew about Pentium 4 would it seem like a miracle.

There was still a major jump from Yonah to Conroe though, it's undeniable. Banias (and the direct shrink Dothan) lagged pretty far behind K8 in outright performance as well as performance per clock, mostly due to starved memory bandwidth and poor SIMD/FP grunt.

While Yonah mostly closed the gap per clock, the highest spec chips were only clocking in around the lowest Athlon X2 counterparts. http://www.anandtech.com/show/1650/7

That said there were PHENOMENAL mobile CPUs though and the fact that they were even in the same ballpark as the Athlon X2 chips is pretty amazing. It still wasn't a given that Intel could get another 25+% IPC boost out of the design as well as crank up the clocks, but that's exactly what they did and what made Conroe such a success.

http://www.anandtech.com/show/1900/11

There was still a major jump from Yonah to Conroe though, it's undeniable. Banias (and the direct shrink Dothan) lagged pretty far behind K8 in outright performance as well as performance per clock, mostly due to starved memory bandwidth and poor SIMD/FP grunt.

While Yonah mostly closed the gap per clock, the highest spec chips were only clocking in around the lowest Athlon X2 counterparts. http://www.anandtech.com/show/1650/7

That's not what your link says. Look again. Those are Dothan Pentium M being compared with. Their IPC is on par with the Athlon 64.

That said there were PHENOMENAL mobile CPUs though and the fact that they were even in the same ballpark as the Athlon X2 chips is pretty amazing. It still wasn't a given that Intel could get another 25+% IPC boost out of the design as well as crank up the clocks, but that's exactly what they did and what made Conroe such a success.

http://www.anandtech.com/show/1900/11

Your link shows Yonah, and IPC was also on par with Athlon 64.

Let me emphasize the base for the 40% IPC increase here

The other thing is Zen really needs to hit something around 4 GHz or higher along with that bump in IPC to be relevant in this year's market. I hope they pull it off; hopefully we'll see soon.

That's not what your link says. Look again. Those are Dothan Pentium M being compared with. Their IPC is on par with the Athlon 64.

Your link shows Yonah, and IPC was also on par with Athlon 64.

It doesn't really matter .. His point is still valid. A 20% IPC increase over yonah, whilst adding extra pipeline stages, (thus significantly increasing frequency headroom to make it a desktop killer as well - something Yonah never would have been ), all without increasing power consumption was a triple- wammy that not many people saw coming.

The other thing is Zen really needs to hit something around 4 GHz or higher along with that bump in IPC to be relevant in this year's market. I hope they pull it off; hopefully we'll see soon.

40%IPC>Ev + 8 cores + SMT @ 4Ghz @ 95w TDP ????

Just to be relevant?

Well if to be relevant you have to basically smash all of Intel's HEDT lineup, in performance [bar the 6950x] and perfomance/watt then sure.. I guess Zen isn't going to be very relevant then :sneaky:

Last edited:

It doesn't really matter .. His point is still valid. A 20% IPC increase over yonah, whilst adding extra pipeline stages, (thus significantly increasing frequency headroom to make it a desktop killer as well - something Yonah never would have been ), all without increasing power consumption was a triple- wammy that not many people saw coming.

It's something AMD should have definitely been paranoid about. Pentium M was able to reach Athlon 64 IPC and performance without an on-die memory controller. Clearly Intel was up to something, and if they ever put an on-die memory controller on their chips... AMD was resting on their laurels competing with Pentium 4 when they should have been going after Pentium M.

Real men may have fabs, but only the paranoid survive. Hopefully AMD is paranoid enough to make Zen competitive.

Last edited:

40%IPC>Ev + 8 cores + SMT @ 4Ghz @ 95w TDP ????

Just to be relevant?

Well if to be relevant you have to basically smash all of Intel's HEDT lineup, in performance [bar the 6950x] and perfomance/watt then sure.. I guess Zen isn't going to be very relevant then :sneaky:

For desktop, if Zen isn't to get crushed by Kabylake. HEDT will need pretty high clocks as well - how high depends on what '40%' really adds up to.

itsmydamnation

Diamond Member

Out of all the market segments desktop quad core is the one amd will care about least. Laptop apu and server derived chips are the targets.For desktop, if Zen isn't to get crushed by Kabylake. HEDT will need pretty high clocks as well - how high depends on what '40%' really adds up to.

HEDT PLATFORM will also cost more outside the processor. HEDT will win at avx256. Everything else is up for grabs right now.

Zen should be around ivy bridge AVX 256 perf per core/clock.

Remember Jim said Zen target clocks are closer to con then they are to cat....

cytg111

Lifer

Except it wasn't really a miracle. Between Pentium 3 and Conroe were Banias, Dothan, and Yonah (ie Pentium M and Core), so there was some guidance as to Conroe's performance. Only if you were living under a rock and only knew about Pentium 4 would it seem like a miracle.

Mobile parts right? As with arm it doesnt automatically mean the arch will/can scale?

IIRC Banias was an evolution of the P3, tad longer pipe, tad better branch prediction, P4 FSB and a buttload(is that boatload?) og powersaving ninja tricks.

Thinking about it.. while the P4 was having a meltdown, over the same timeframe it could be interesting to see Pentium-M's performace/IPC increase over Banias->Dothan->Yonah->Core .. may it just fit the same performance increments that we've been seeing ever since? (excluding jump at nehalem, however that one was sipping another 50 watts or so right?)

So we have an evolution of a arch that is desktop(Pentium-x) -> mobile(Penitum-m) -> desktop(core) -> mobile(core-m).

So historically we're in for the next big desktop thing 🙂.

I am of the view that first generation zen will focus more on servers than desktops. Servers can give them much more money compared to desktop. Even if the architecture is capable to reach clocks like 4.8GHz, the 14nm LPP wouldn't be able to reach those clocks as of now.For desktop, if Zen isn't to get crushed by Kabylake. HEDT will need pretty high clocks as well - how high depends on what '40%' really adds up to.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-