A statistical approach: We might have seen a benchmark residing on the tail of the distribution. Let's wait for more samples (not ES).Now we have established some kind of agreement that a 95w tdp ~180mm2 cpu on a low freq process is not 2% faster than a 140w tdp 240mm2 die on a high freq process costing 1100 usd.

It would be a bit more interesting - to say the least - if we got some info about the efficiency.

The writes about it is very slim imo in relation to its crucial importance.

Regarding die size:

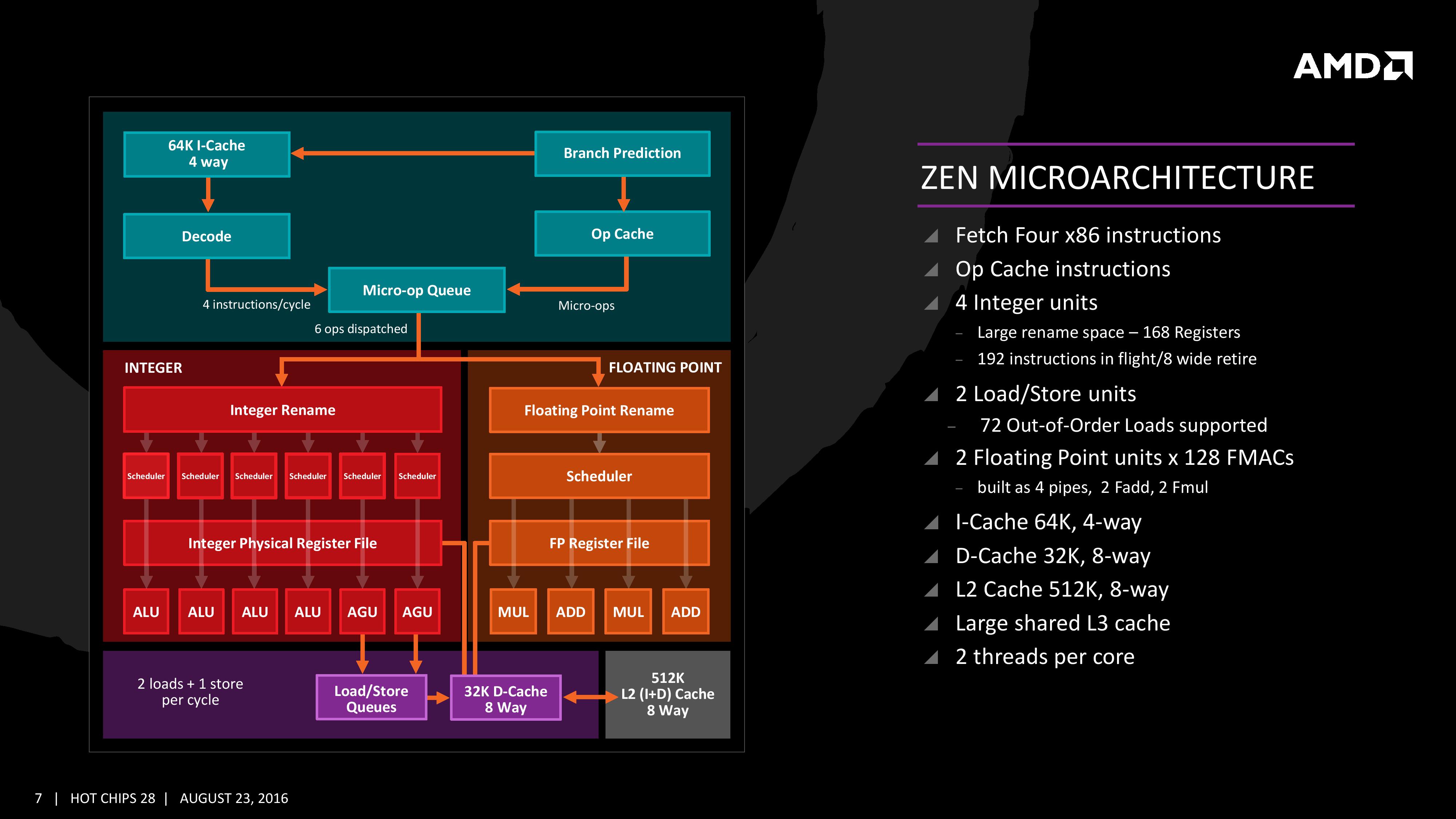

AMD left out a lot of logic related to Intel's powerful 2x256b SIMD bandwidth (from caches to EX). And they do this 8 times per Zeppelin die.

Also some article mentioned, that they use a high density variant of the process (not sure, if they mean SoC density metal layers or HD libs). But this would both stand for small die size and power efficient (knee of the curve) clockability in the high core count range.