ISA-wise the first to die when RISC-V generally becomes available will be POWER and ARM.

Tenstorrent, Ventana, SiFive/StarFive, Full China(HiSilicon, T-Head, CAS), etc. All are targeting HPC/XCC first and any fall down to HEDT is going to slap POWER and ARM first.

RCS Blackbird >5000 USD

Avantek ARM Desktops >7000 USD

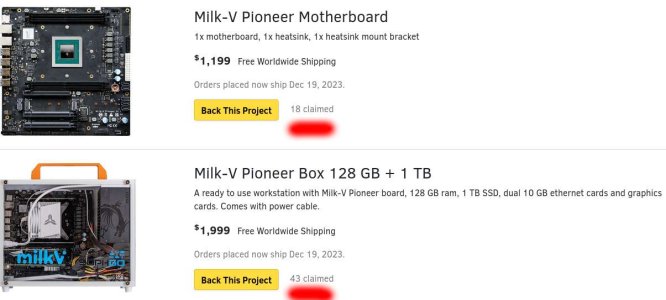

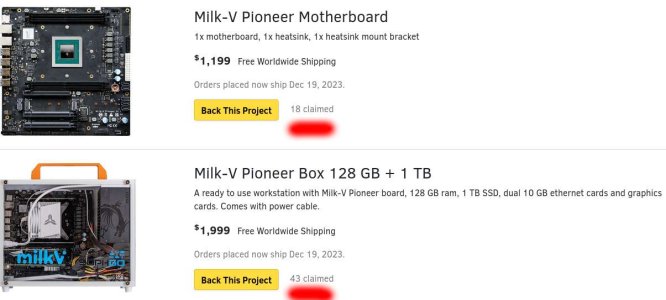

versus whatever replaces this in production:

Whereas the lower-end is just ARM, with RK3588/Kompanio 1380(Genio 1200 will get hit harder than the 1380 part) will probably have to deal with:

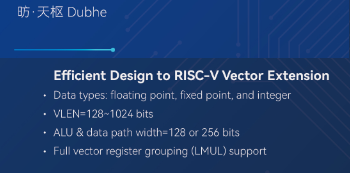

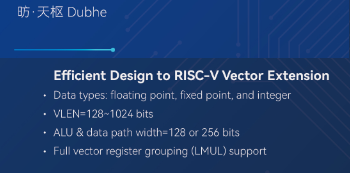

TH1520 (4x C910(OpenT-head)) // now -> JH8100 (4 Dubhe(weak si5 670?) cores/2?-4? Merak(weak si5 470?) cores) // Q2 2024

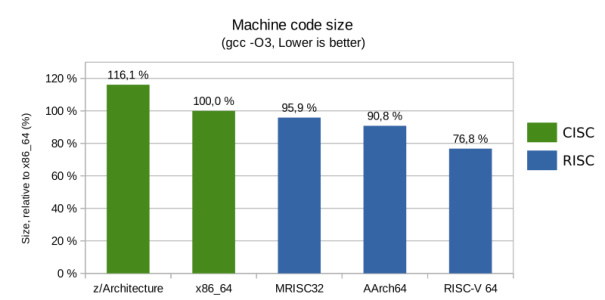

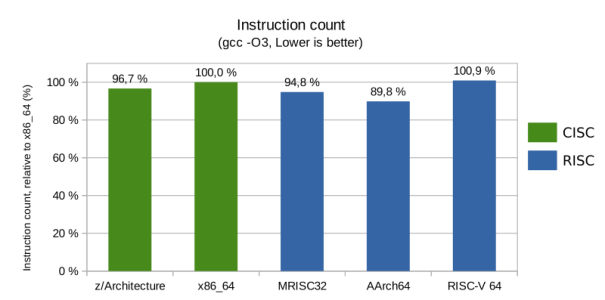

The general consensus for x86 death is how much lower cost RISC-V will be for each market segment.

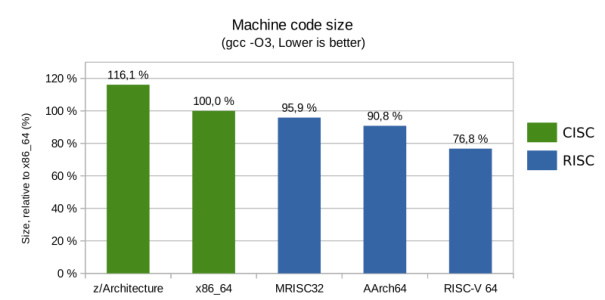

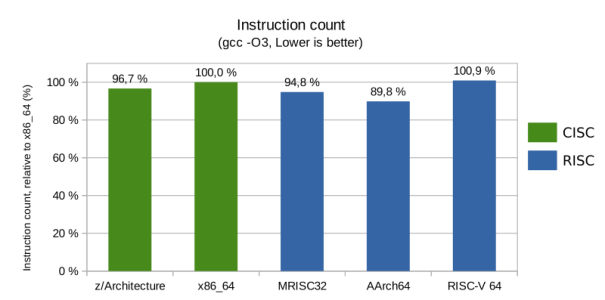

Every bit counts, and Intel isn't helping with x86 future proofing.

APX reduces code density as REX2 is larger than REX, AVX10 falls into prefix determined vector-width which for future code means low code density/high instruction count.

For example, Dubhe/Merak should be able to unroll VLA-like code to full width like Xuantie910/C910/C920 cores. Instead of a couple 8x128-bit/4x256-bit non-dependent/parallel instructions, it can just launch one 1024-bit for density.

I'm pretty confident that Dubhe is based on p670 and Merak is based on p470 now:

It is more likely Intel if they see ISA death(Intel now >$50B for x86 sales(per-year) -> IBM-like future <$7B for x86 sales(per-year)), they would just accept it and full run RISC-V in IFS. [Someone tell SiFive to launch a P800 on 20A/18A, with the level of board support that StarFive gets, yeesh~. P550 dev board looks awful.]

More ISA specific:

www.bitsnbites.eu

RV64+C. If any of the software (liblz4, sqlite3, mfat, mxml, quake) op'd for SIMD-scaling. Where RV64V can be inserted reducing instruction count. Like unlimited SIMD scaling portions where 16x RV64C instructions can be fused into one 1024-bit RV64V instruction. Ins. count reduction -> higher code density for HPC/High-end workloads. REX2(APX) and Enhanced EVEX(AVX10) appear to make the above worse.