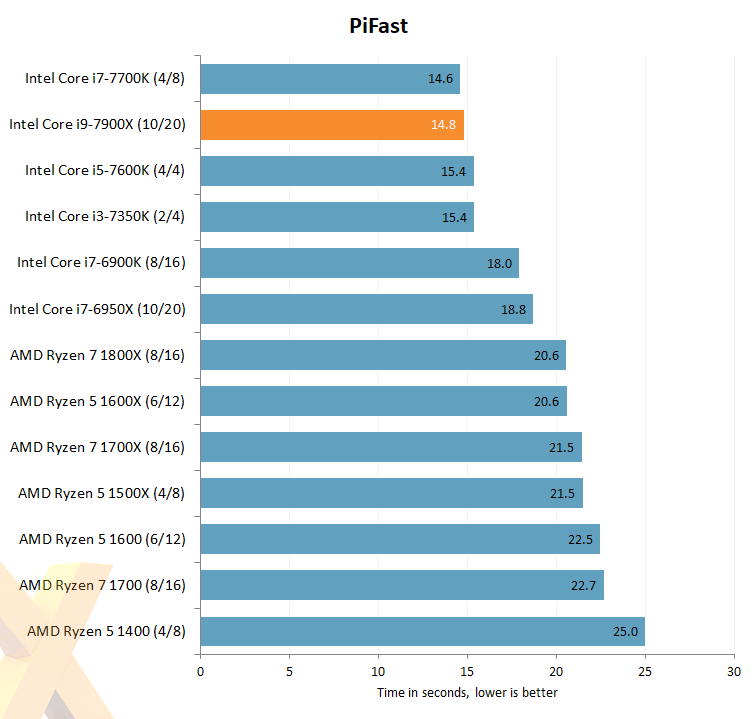

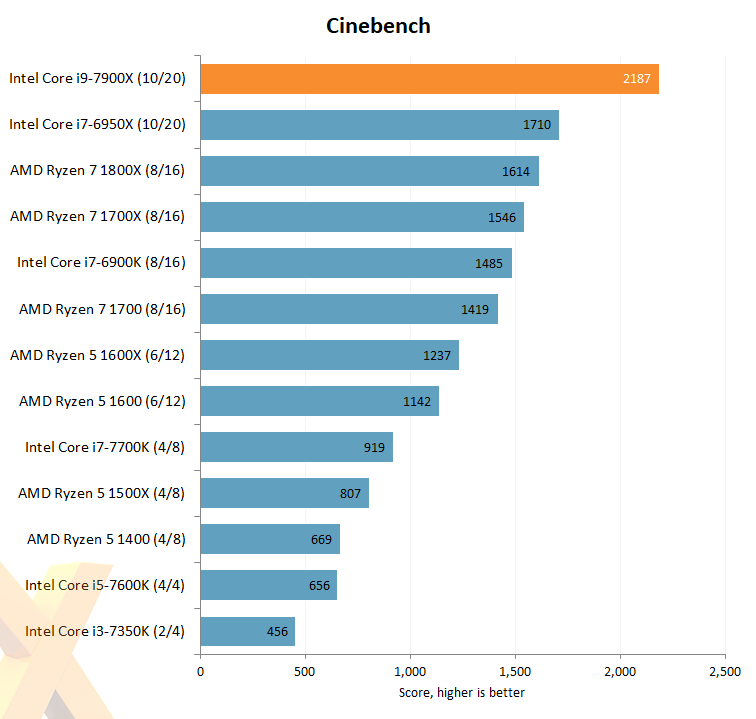

In apples to apples it is ~10% ST in Cinebench.

https://www.extremetech.com/computi...-reviewed-taking-fight-intel-mid-range-market

I like this review cause it is running both contenders as people would run them ~DDR3200 and one can see the following interesting points:

1) 7500 with DDR4

@2400 gets destroyed by SMT enabled 7700K with 3200 mem. 7700 is almost

TWICE as fast in some of the tasks.

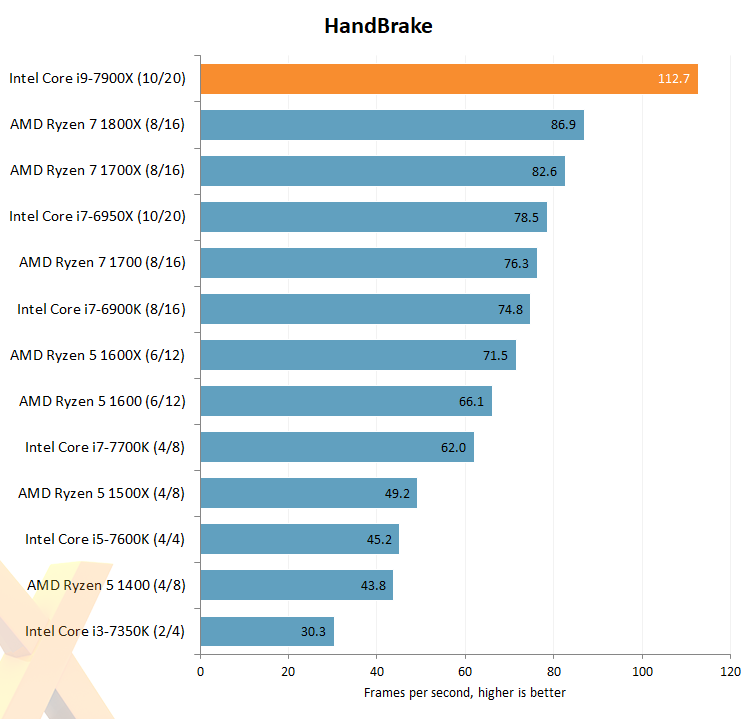

2) Handbrake tests show that program is coded to make use of Intel's CPU resources in vector processing ( full 256bit path ), Ryzen has quite a disadvantage here. So 8 core RYZEN vs 8 core Intel will be at same IPC dissadvantage in those types of apps.

3) Something in Dolphin emu code does not like Ryzen CPU, giving Intel unexpected IPC advantage ( one that could go away with some optimization ).

4) And in games results speak for themselves, 3200 mem equipped 7700K is a beast that is up to 50% faster. ( i know all frames rates are "playable" but CIV turn speed or EU4 sim speed matters)