Coral Rapids won't compete with Venice, it will compete with whatever AMD develops after Venice for 2028NV already announcing upcoming Vera CPU comes with SMT, guess it is the feature eventually comes to all CPU.

And I really don't understand why we are debating such issue when Intel is leaking CRR with SMT to compete with Venice which comes with 512 threads. Intel know upcoming DMR with 256T cannot compete with Venice in MT. Does the math fail you?

How about I am predicting all future ARM SoC, be it client or server CPU are all coming with SMT. Do you want to argue with it?

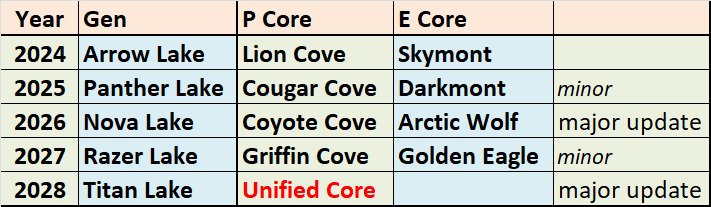

Discussion Intel Nova Lake in H2-2026: Discussion Threads

Page 31 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,476

- 11,197

- 106

that's called FlorenceCoral Rapids won't compete with Venice, it will compete with whatever AMD develops after Venice for 2028

Wouldn't be surprised if it's the last P-coreCoral Rapids is based on Unified Core though which we don't know anything about.

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,476

- 11,197

- 106

Unified Core is 2029+ so unlikely.Coral Rapids is based on Unified Core though which we don't know anything about.

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,476

- 11,197

- 106

more cores/cache/power/etc would work just fine.Griffin is like a mid improvement over Panther Cove i doubt it would do any good in 2028.

Not like they have any chances in server anyhow.

igor_kavinski

Lifer

- Jul 27, 2020

- 28,173

- 19,210

- 146

I'm expecting AMD to set MSRP of at least $799 for their 48 thread part so Intel may target a similar price point. Their excuse will be obviously, we are giving you a taste of HEDT on your mere desktop!

So you believe that the TCO for a server is heavily influenced by the price of the processor?Depends on the definition of spitting distance. Half the total performance or better for half the price is what Ampere's latest looks like - https://www.servethehome.com/ampere...permicro-nvidia-broadcom-kioxia-server-cpu/2/

ARM could implement SMT on all their Neoverse offerings if their customers were asking for it. They aren't asking for it. It is fair to argue that they're not asking for it because AMD and Intel provide an acceptably priced option for servicing that market. But if SMT really was the best thing ever they wouldn't be ignoring it.

In reality, having DOUBLE the number of physical servers to compete with SMT enabled x86 servers likely costs the company 5-10x more over the life of the product for many reasons (my SWAG).

Arguing against SMT is pointless IMO. Arguing against higher performance on the basis of cpu costs? With that logic, why not use a bunch of $1.00 ARM M0 cores?

with the wafer price increase expect $900-1000 USDI'm expecting AMD to set MSRP of at least $799 for their 48 thread part so Intel may target a similar price point. Their excuse will be obviously, we are giving you a taste of HEDT on your mere desktop!

Coral Rapids won't compete with Venice, it will compete with whatever AMD develops after Venice for 2028

Well, we now know how Intel will survive (Tax payer money). BTW, As an American, I think this is a good idea.that's called Florence

My concern is that Intel could easily become lackadaisical with a steady influx of US government money keeping it solvent.

With the current roadmap, it is difficult to see how Intel "gets its groove back".

I was hoping that Intel could do a few tweaks to lower latency between tiles which might free up a good deal of performance .... we will see.

Tariffs are currently going to raise prices; however, both a district court, and now a Federal Appellet court have ruled that most (including the chip tariffs) tariffs imposed as "recipricol" are not constitutional. It is likely this will be addressed by the Supreme court by June 2026.with the wafer price increase expect $900-1000 USD

I think it likely the Supreme court will uphold the prior 2 rulings. The BEST case would be for SCOTUS to rule that "Tariffs" are "Taxes" and require the US Congress to pass laws to change them.

Of course, pricing has a nasty way of going up IMMEDIATELY and taking quite some time to go back down

Not just Money they need 1-2 good fables customer as well for Fab learning Curve they need to get both their fab and design S*** together.Well, we now know how Intel will survive (Tax payer money). BTW, As an American, I think this is a good idea.

This is incorrect for Zen5. Zen5 have whole front-end statically partitioned, it has decoders, op-cache and so on duplicated for each thread. They use significant amount of silicon just for smt which ain't used fot 1t at all.

Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,592

- 739

- 126

Anyone still doubting that 52C on DT will happen?

What about all the talk on this forum from some people saying that no company will release such a CPU on the consumer market? They'll have to buy expensive HEDT / server / whatever if they want it. Too low mem bandwidth to feed the threads, no use cases for it, bla bla.

Anyone still doubting that 52C on DT will happen?

What about all the talk on this forum from some people saying that no company will release such a CPU on the consumer market? They'll have to buy expensive HEDT / server / whatever if they want it. Too low mem bandwidth to feed the threads, no use cases for it, bla bla.

So are you gonna buy it? Run Cinebench all day?

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,250

- 7,049

- 136

Anyone still doubting that 52C on DT will happen?

What about all the talk on this forum from some people saying that no company will release such a CPU on the consumer market? They'll have to buy expensive HEDT / server / whatever if they want it. Too low mem bandwidth to feed the threads, no use cases for it, bla bla.

I didn't doubt it, just the utility of it. I doubt they will come cheap. What will power draw be like? Always seemed like a very niche use case. People barely bother with 12/16 core Zen.

Last edited:

Saylick

Diamond Member

- Sep 10, 2012

- 4,117

- 9,627

- 136

Well, here's to hoping that Zen 6 addresses that and allows for 1T to use the full front-end, but I digress. This is the Intel Nova Lake thread, after all.This is incorrect for Zen5. Zen5 have whole front-end statically partitioned, it has decoders, op-cache and so on duplicated for each thread. They use significant amount of silicon just for smt which ain't used fot 1t at all.

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,476

- 11,197

- 106

Nope, they're all watermarked.Zen5 have whole front-end statically partitioned, it has decoders, op-cache and so on duplicated for each thread.

Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,592

- 739

- 126

Yes, and will run productivity Sw and more.So are you gonna buy it? Run Cinebench all day?

But it does not matter what I’ll run. What matters is that it’ll be released for consumer DT in general.

You still doubt it’ll be released, or you admit your arguments against that happening were overruled by Intel (and AMD who will be releasing a similar 48/50T Zen6 CPU on DT)?

Last edited:

Fjodor2001

Diamond Member

- Feb 6, 2010

- 4,592

- 739

- 126

150W TDP according to spec. Yes more at peak, but still in relation to current TDP.I didn't doubt it, just the utility of it. I doubt they will come cheap. What will power draw be like? Always seemed like a very niche use case. People barely bother with 12/16 core Zen.

Good that you did not doubt it happening, many other on the forum did for non-valid technical reasons.

Sure not everyone will use all cores at the beginning. But it’s a top SKU driving perf forward, so enthusiasts will pave the way and Average Joe will follow later. Not many were using 6/8C when they were first introduced either, but pioneers pushed the boundaries and now it’s mainstream. Same will happen now.

adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,476

- 11,197

- 106

16c has been on the market for like 6 years and it's completely irrelevant to this day.Not many were using 6/8C when they were first introduced either, but pioneers pushed the boundaries and now it’s mainstream

AMD says SMT is 5% of the die... so it's a pretty good use of space IMO.This is incorrect for Zen5. Zen5 have whole front-end statically partitioned, it has decoders, op-cache and so on duplicated for each thread. They use significant amount of silicon just for smt which ain't used fot 1t at all.

I certainly don't doubt (and never have) that Intel intends to release it. In fact, it has been my contention that Intel is going to market the crap out of it. Core count in the age of the Arrow Lake class architecture will be the equivalent of MHz in the age of Netburst.Anyone still doubting that 52C on DT will happen?

What about all the talk on this forum from some people saying that no company will release such a CPU on the consumer market? They'll have to buy expensive HEDT / server / whatever if they want it. Too low mem bandwidth to feed the threads, no use cases for it, bla bla.

Back in the day, AMD simply moved to model numbers that were created to show equivalent P4 clock speeds the AMD chip was performance equal to.

Not sure how one does such a thing with cores. Perhaps there is a general performance model number and a "Cine-performance" model number

To be clear, AMD is releasing a 24c/48t Zen 6 on the desktop. I think there is word of LPE cores built into the IOD on the laptop processor (replacement for Strix Halo). If such a laptop processor was created, it would technically have 26c/52t if it had 2x12c CCD's connected with an IOD that contained 2 LPE Zen 6.You still doubt it’ll be released, or you admit your arguments against that happening were overruled by Intel (and AMD who will be releasing a similar 48/50T Zen6 CPU on DT)?

... and I am also of the opinion that this is a solution in search of a problem.

For people who actually utilize the kinds of programs that CB is designed to benchmark for, they will shell out the $$ for a Thread ripper that not only has lots more cores, but also has lots more bandwidth that these real world programs rely on.

Just my opinion though.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.