Discussion Intel Nova Lake in H2-2026: Discussion Threads

Page 30 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Covfefe

Member

- Jul 23, 2025

- 101

- 180

- 76

What? They took out SMT with LNC and now PNC, the point is that LBT saw DMR without SMT and knew it immensely hurt their competitiveness with Venice. Nothing in the letter even implies that Granite Rapids is the generation bringing back SMT. Why would the CEO announce bringing back a feature to DCAI products that hasn’t even left the segment yet, and launched before his tenure?

The "this" in the second sentence of that paragraph refers to the act of gaining marketshare through GNR.

To support [regaining share as we ramp Granite Rapids], we are reintroducing simultaneous multi-threading (SMT).

It's not that deep. He's saying it because it sounds good.

Tan was refering to it's removal in Diamond Rapids most likely.

LightningZ71

Platinum Member

- Mar 10, 2017

- 2,679

- 3,377

- 136

The last time that I read something extensive about it was here at AT. I'd have to go digging in the internet archive to find it again, but they had a color coded comparison of the processor functional units showing what was unique, what was shared, what was partitioned, and what was wholely duplicated.Could you link your source for the breakdown what is statically partitioned, what is watermarked and what is shared for HT? In AMD case that information is in software optimization guide among other sources. Is that true for Intel too?

coercitiv

Diamond Member

- Jan 24, 2014

- 7,471

- 17,853

- 136

Sounds really good:It's not that deep. He's saying it because it sounds good.

That's exactly what a CEO wants to do, invent a non-existent reason to talk about his company losing competitive advantage.Moving away from SMT put us at a competitive disadvantage.

You know that it is the reason they are not confident with DMR on winning all the benchmarks a single feature lmao.That's exactly what a CEO wants to do, invent a non-existent reason to talk about his company losing competitive advantage.

moinmoin

Diamond Member

- Jun 1, 2017

- 5,248

- 8,463

- 136

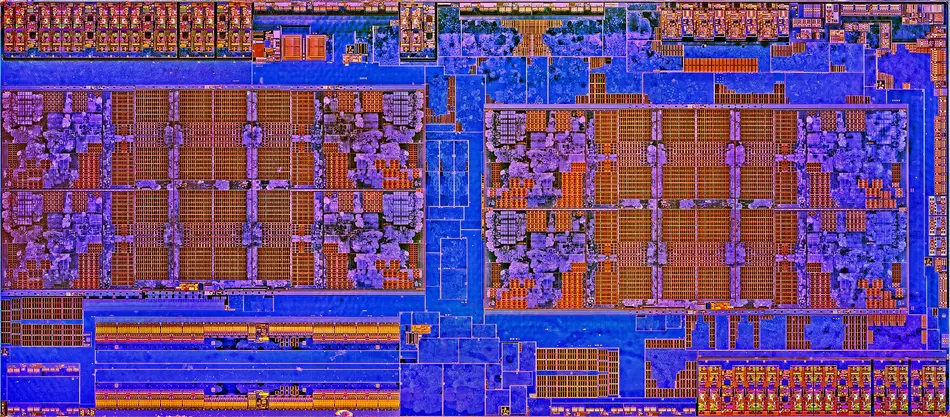

Even with the first implementation in Zen 1 most of it was already competitively shared though.The last time that I read something extensive about it was here at AT. I'd have to go digging in the internet archive to find it again, but they had a color coded comparison of the processor functional units showing what was unique, what was shared, what was partitioned, and what was wholely duplicated.

Zen - Microarchitectures - AMD - WikiChip

Zen (family 17h) is the microarchitecture developed by AMD as a successor to both Excavator and Puma. Zen is an entirely new design, built from the ground up for optimal balance of performance and power capable of covering the entire computing spectrum from fanless notebooks to high-performance...

en.wikichip.org

en.wikichip.org

- Red - Competitively shared structures

- Turquoise - Competitively shared and SMT tagged

- Blue - Competitively shared with Algorithmic Priority

- Green - Statically Partitioned

Server is where the highest margins are. Server is where the highest growth is. Removing features like SMT and AVX512 was an unmitigated disaster for Intel from a financial standpoint.That particular part of that quote doesn't make sense. Intel only dropped hyperthreading on Arrow Lake and Lunar Lake. The lack of SMT is pretty low on the list of issues with those CPUs. Server is where SMT matters the most, and they haven't dropped it for any server products. That reads to me as Lip Bu Tan trying to distance himself from his predecessor.

.. and that is relevant how? Intel proclaiming that they shouldn't have removed SMT seems like pretty conclusive evidence that the removal was a mistake .... don't you think?Not out yet.

That may be less of a problem in server than it is in desktop. In server, the processor is often power constrained by the socket power limits, or thermally limited by the density of the cores in the package.Really I wouldn't expect Intel to be competitive in server again until they commit to TSMC.

While I don't expect Intel's 18A to clock anywhere near as high as TSMC's N2, I suspect 18A will be very power efficient. This could make for some very nice high core count DC products ..... which is why I am so distraught that Intel botched the architecture by removing SMT and AVX512.

My thoughts are:Process node is the least of their problems in server.

1) Lack of SMT

2) High latency between chips

3) Lack of AVX512

I actually think 18A is going to be a pretty good server process ..... but GOD AWFUL expensive.

In my management positions over the last 20 years, I have always argued against layoffs of engineers:Every layoffs bleeds talent

1) A factory selling its production gear is doomed.

2) Sure, you tend to layoff your worst performers (God have mercy on you if you start laying off by highest salary). That in, and by itself, is just making the company more efficient. The issue is that it scares the bejesus out of all employees. IME, you lose about 5-10% of your best people as well. The ones that are the most marketable and highest performing also leave when you do engineering layoffs.

DMR has AVX-512 as for High latency we will see with DMR it's unknown1) Lack of SMT

2) High latency between chips

3) Lack of AVX512

Intel has always had AVX-512 on servers since Skylake Xeons on all P-core server stuff. DMR will have AVX512/AVX 10.2 too.which is why I am so distraught that Intel botched the architecture by removing SMT and AVX512.

My thoughts are:

1) Lack of SMT

2) High latency between chips

3) Lack of AVX512

Only E-core server stuff of SRF and CWF don't have AVX512.

If E-core based RRF happens in 2027 it will have AVX512/AVX10.2.

Thunder 57

Diamond Member

- Aug 19, 2007

- 4,250

- 7,049

- 136

Intel has always had AVX-512 on servers since Skylake Xeons on all P-core server stuff. DMR will have AVX512/AVX 10.2 too.

Only E-core server stuff of SRF and CWF don't have AVX512.

If E-core based RRF happens in 2027 it will have AVX512/AVX10.2.

The problem with CWF is the lack of SMT. It could be a tough sell.

It has 288Cores the problem I see is the launch schedule it's too damm close to Venice dense if it had come out this year it would have been fine.The problem with CWF is the lack of SMT. It could be a tough sell.

The problem with CWF is the lack of SMT. It could be a tough sell.

The earlier E core server products didn't sell at all. I think that's where the cancellation rumors came from.

The people buying Intel still at this point are buying the P core.

LightningZ71

Platinum Member

- Mar 10, 2017

- 2,679

- 3,377

- 136

Those are the diagrams that I was thinking of, but it's not the information I was looking for. I think I am confusing two separate articles. I remember HotHardware had a good one and someone else had one that addressed a characteristic of AMD's implementation that was giving them more efficient resources allocation.Even with the first implementation in Zen 1 most of it was already competitively shared though.

Zen - Microarchitectures - AMD - WikiChip

Zen (family 17h) is the microarchitecture developed by AMD as a successor to both Excavator and Puma. Zen is an entirely new design, built from the ground up for optimal balance of performance and power capable of covering the entire computing spectrum from fanless notebooks to high-performance...en.wikichip.org

AMD has an update for Zen 5 at https://www.amd.com/en/blogs/2025/simultaneous-multithreading-driving-performance-a.html

- Red - Competitively shared structures

- Turquoise - Competitively shared and SMT tagged

- Blue - Competitively shared with Algorithmic Priority

- Green - Statically Partitioned

View attachment 129504

View attachment 129505

The core count(288) is there though especially on 2S (576 cores). It should be a decent part for Cloud though it's likely not as versatile as Turin D in lots of other workloads. Has other issues as well like the launch delay, and perhaps slow L3 cache bottle-necking performance. Have to wait for reviews to see how well it performs and scales.The problem with CWF is the lack of SMT. It could be a tough sell.

At least till now E-core team has been focused on optimizing area and IPC. SMT hasn't been a focus of E-core guys throughout.

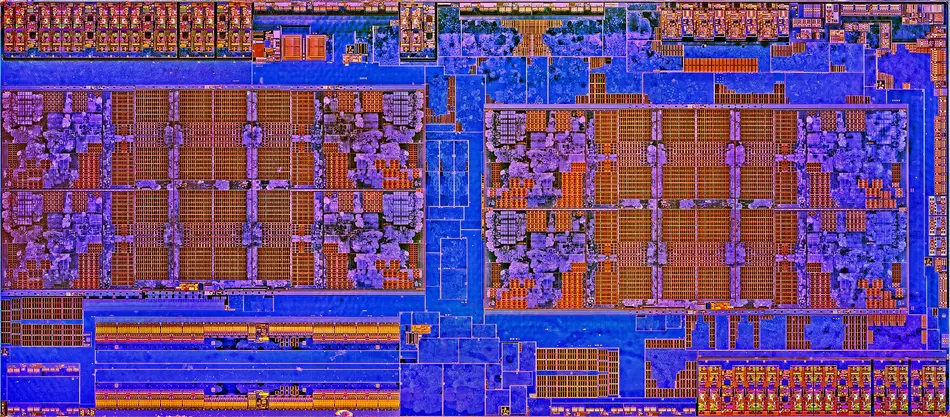

Those are the diagrams that I was thinking of, but it's not the information I was looking for. I think I am confusing two separate articles. I remember HotHardware had a good one and someone else had one that addressed a characteristic of AMD's implementation that was giving them more efficient resources allocation.

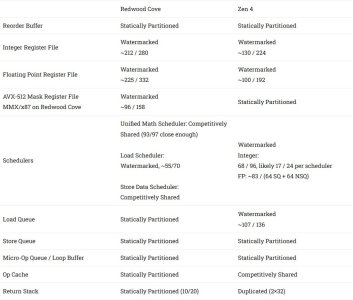

did you mean this one by chance? source is C&C https://chipsandcheese.com/p/intels-redwood-cove-baby-steps-are-still-steps

It will be interesting to see how DMR competes with Venice (non D). Anyone have any idea how many cores Venice (non D) will have?DMR has AVX-512 as for High latency we will see with DMR it's unknown

Only E-core server stuff of SRF and CWF don't have AVX512.

for cloud computing, more threads will matter. Considering the target market of CWF, the lack of SMT makes it likely that Venice D will best it by quite a bit.The problem with CWF is the lack of SMT. It could be a tough sell.

Agree. Against Turin D, CWF looks very good. Against Venice D .... not so much.It has 288Cores the problem I see is the launch schedule it's too damm close to Venice dense if it had come out this year it would have been fine.

It still has to compete with a 2S Venice D which will be sporting 512c/1024t. Last round, Intel's 2S offering wasn't impressive. Hopefully they have worked out whatever issue they had going on with the last Xeon's.The core count(288) is there though especially on 2S (576 cores). It should be a decent part for Cloud though it's likely not as versatile as Turin D in lots of other workloads. Has other issues as well like the launch delay, and perhaps slow L3 cache bottle-necking performance. Have to wait for reviews to see how well it performs and scales.

At least till now E-core team has been focused on optimizing area and IPC. SMT hasn't been a focus of E-core guys throughout.

Nobody was saying that past autumn 2020 when vaccines became available en masse, and Pat got his job in Feb 2021.

He bet a lot on High NA which clearly isn't a magic wand he wanted it to be.

Covid theater continued way past autumn 2020, work from home was still promoted for another 1-1.5 years.

Just past the peak of the mass psychosis Intel exec was still saying this in January 2023:

On penetration. There is huge upside for us in emerging markets. I have myself lived in Asia for many years, Middle East as well. That’s the areas where we see growth, and this is where we expect growth to come. And then maybe if I bring all of this a little bit together, a little bit of a personal anecdote, I’ll talk about my daughter, Maya. She’s 20 years. She’s in college, a junior in college. And she always had access to PCs, given what I’m doing for a job — for a living, and she never looked at them until COVID hit. And all of a sudden, she understood that consuming education content on a tablet, consuming it on a mobile phone is really not cool.

And so she lobbied me not to buy her 1 laptop but 2 because she was really concerned about not being able to dial in. So she wanted to have — if 1 unit went down, she wanted to have 2. And that, I think, is a customer segment that was not looking at PCs prior to the pandemic and is now a very core part of what we are planning with. So I hope that gives you a bit more color and explains why we are bullish about the growth.

Christoph Schell, Chief Commercial Officer

These types of stories were behind unrealistic TAM estimates:

Intel Roadmap and PC TAM Update – Tone Deaf, Out Of Touch, Living In a Fantasy World, or Disconnected From Reality?

Intel held their PC TAM (total addressable market) and Roadmap Update event online yesterday.

Will it? If SMT matters so much for cloud, then why exactly do none of the custom ARM processors deployed by AWS, Azure, Google and Alibaba have SMT? It's not like ARM is incapable of offering a core design with SMT.for cloud computing, more threads will matter. Considering the target market of CWF, the lack of SMT makes it likely that Venice D will best it by quite a bit.

I'm not saying that cloud providers don't want to have some instance types with SMT - for certain workloads it is advantageous and their customers will want it. But for plenty of cloud instance types SMT is going to provide zero benefit. Some instance types even hard disable it.

LightningZ71

Platinum Member

- Mar 10, 2017

- 2,679

- 3,377

- 136

I hadn't seen that particular chart before, but that addresses what I was talking about.View attachment 129522

did you mean this one by chance? source is C&C https://chipsandcheese.com/p/intels-redwood-cove-baby-steps-are-still-steps

LightningZ71

Platinum Member

- Mar 10, 2017

- 2,679

- 3,377

- 136

ARM itself currently only offers three cores with SMT: Neoverse-e for network edge and a pair of A65e variants for specific markets that use it more for compute verification purposes. A big issue for SMT is that it is often performance indeterminate in that a thread can run on the same core with the same data and perform differently depending on what the other thread is up to. That behavior is unpopular in ARM world. It also increases cache pressure and can make core power draw less predictable.Will it? If SMT matters so much for cloud, then why exactly do none of the custom ARM processors deployed by AWS, Azure, Google and Alibaba have SMT? It's not like ARM is incapable of offering a core design with SMT.

I'm not saying that cloud providers don't want to have some instance types with SMT - for certain workloads it is advantageous and their customers will want it. But for plenty of cloud instance types SMT is going to provide zero benefit. Some instance types even hard disable it.

None of that is a show stopper, but it IS a complication that brings only limited performance gains. Intel and AMD (and IBM for different reasons) chose to use it because they are deep, experienced CPU houses that have the resources to handle the headaches for the benefits, and even Intel balked at it for a segment or two.

He's much more likely to make this type of decision based on (updated) reports from engineering teams. You need to keep in mind the information LBT received may not necessarily be the same as Pat. (due to changes in company environment and structure, updates in simulations etc.)

Also, as @Darkmont quote said, he is looking for new head of datacenter division. It means he is not exactly satisfied with the leadership in place.

SMT provides the best performance for the transistor budget of anything I can think of.Will it? If SMT matters so much for cloud, then why exactly do none of the custom ARM processors deployed by AWS, Azure, Google and Alibaba have SMT? It's not like ARM is incapable of offering a core design with SMT.

I'm not saying that cloud providers don't want to have some instance types with SMT - for certain workloads it is advantageous and their customers will want it. But for plenty of cloud instance types SMT is going to provide zero benefit. Some instance types even hard disable it.

Currently, there aren't any ARM servers that can come within spitting distance of x86 that I have seen (someone feel free to show me a benchmark that proves me wrong here).

The reason ARM is popular isn't because it is performant, it's because it is cheep when you are someone like Amazon that can make your own custom variant and deploy a metric crap ton of servers all within your own company.... and optimize your server software just for that hardware (among other things a monolith like Amazon can do that other companies can't).

Depends on the definition of spitting distance. Half the total performance or better for half the price is what Ampere's latest looks like - https://www.servethehome.com/ampere...permicro-nvidia-broadcom-kioxia-server-cpu/2/Currently, there aren't any ARM servers that can come within spitting distance of x86 that I have seen (someone feel free to show me a benchmark that proves me wrong here).

ARM could implement SMT on all their Neoverse offerings if their customers were asking for it. They aren't asking for it. It is fair to argue that they're not asking for it because AMD and Intel provide an acceptably priced option for servicing that market. But if SMT really was the best thing ever they wouldn't be ignoring it.

NV already announcing upcoming Vera CPU comes with SMT, guess it is the feature eventually comes to all CPU.Depends on the definition of spitting distance. Half the total performance or better for half the price is what Ampere's latest looks like - https://www.servethehome.com/ampere...permicro-nvidia-broadcom-kioxia-server-cpu/2/

ARM could implement SMT on all their Neoverse offerings if their customers were asking for it. They aren't asking for it. It is fair to argue that they're not asking for it because AMD and Intel provide an acceptably priced option for servicing that market. But if SMT really was the best thing ever they wouldn't be ignoring it.

And I really don't understand why we are debating such issue when Intel is leaking CRR with SMT to compete with Venice which comes with 512 threads. Intel know upcoming DMR with 256T cannot compete with Venice in MT. Does the math fail you?

How about I am predicting all future ARM SoC, be it client or server CPU are all coming with SMT. Do you want to argue with it?

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.