Are you really laughing your ass off? If so please tell me what you're on so I can get some of that!

oooh you cussed, telling the mods, that's a no-no word /s

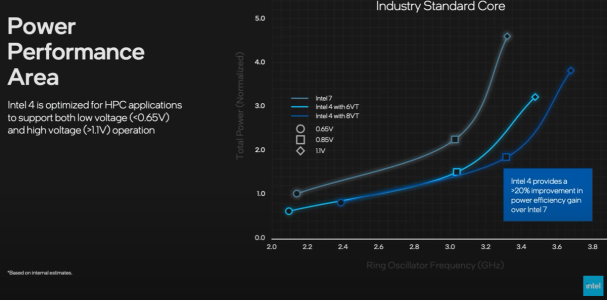

But yes, I do find it hilarious that you think that me pointing out how you are not mentioning one of the three most important aspects of chip design, you know, the whole PPA shtick- area, and only saying, "wow look at how high perf RPC is, what a good core wowee"- is me twisting your words or anything.

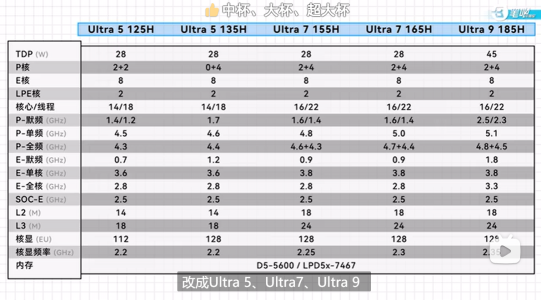

Zen 4 and Golden Cove architectures are very comparable when it comes to IPC. While we don't know the exact numbers I bet the total numbers of transistors are in the same ballpark as well

The problem is that design isn't just "transistor count". Usage of HP vs UHP vs HD is another aspect- and Intel has shown that they are unable to use dense cells while esentially the rest of the industry is transitioning to higher density cells, where sure you lose a bit of peak clocks, but you gain a bunch in area (and thus lower leakage) while also being able to get massive IPC cores without blowing up the cores.

In fact, I suspect that they used a lot of HD cells in PLMC (which is why density was actually comparable to Zen 2), and look how that turned out. There's a reason why SNC is

so much larger than PLMC, while transistor density between 10nm and 10nm+ did not change according to Techinsights.

Also, idk what you mean by "in the same ballpark", but I don't think GLC has a similar transistor count as Zen 4. Just look at the structure sizes, GLC has way larger structure sizes in many aspects compared to Zen 4.

Which of course means the difference in transistor density is mainly a result of the superior TMSC process vs Intel 7.

Doubt

AMD has an area advantage over Intel but it is mainly due to the superior process upon which their parts are fabricated compared to Intel.

Look at Zen 3 vs GLC. GLC is ~20% performant, ~ as efficient, but like 75% larger. Both on 7nm nodes.

Look at RWC vs Zen 4. ~performance, let's say ~20% more efficient (I don't think it will be, but am highballing it a lot) but then ~40% larger. This one honestly isn't

as bad, but still...

Equalize the process, Intel cores are still disproportionately larger than what their performance or efficiency gains give it. This hurts them- a lot- especially in server.

Btw, all this, it's just core design. Intel's design throughout the rest of the chip is just as important... and looks to be just as poor. Intel's poor L3 subsystem is pretty sad, and this is especially apparent in server too (look at SPR's L3 bandwidth and latency problems). And look at the even poorer silicon area efficiency of SPR vs Milan, or even GNR vs Genoa. It's

really bad.