Okay, so time for another round of Intel delays. This actually isn't new news, but it kinda changes my opinion...

Raising mobility through the use of non-silicon materials in the transistor channel remains a favored theme with Gargini but he appeared to push back the prospect of deployment until about 2020.

Gargini, discussed compound semiconductor on silicon, as he has done before. But he also discussed the arrival of multi-gate HKMG III-V devices on silicon substrates arriving by 2020. However he also discussed the need to optimize for power consumption rather than performance.

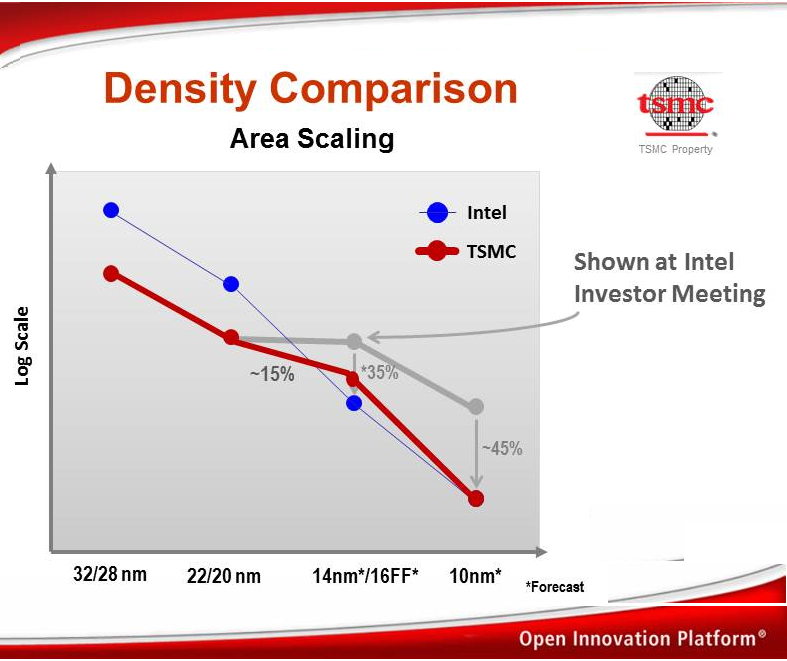

2020 looks, certainly by their 2 year roadmap they had up to 2012/2013, like 7nm for III-V. It is very hard, like this also shows:

http://spectrum.ieee.org/semiconductors/design/changing-the-transistor-channel.

So unless it was just a general, vague statement to avoid spoilers, which actually isn't rare in this industry I guess, I and others like Kanter may be wrong and disappointed when 10nm arrives at last.

Note, BTW, that EUV was also aimed for 10nm.

http://www.eetimes.com/document.asp?doc_id=1266393

However, the articles seems credible if you read some more of it. E.g.

At the same event a year before Gargini had said that compound semiconductors in silicon could be an option in 2015.

For example, they're talking about leakage as a major problem. A more recent interview, with Mark Bohr from 1 year ago:

At very low leakage, you are limited by band-to-band tunneling. Sub-threshold leakage may be more of a problem with some III-V materials. So developing a universal, or widely useful, transistor from high performance to very low leakage is quite a challenging task.

Also, in the EETimes article they're talking about InSb, but it's quite possible that Intel has since then decided to use InGaAs. Note, BTW, that Bohr is talking in the follow-up question specifically about

other companies, which implicitly implies that Intel does have it ready for 10nm.

Other companies may choose to push out the adoption of III-V, because all of the problems have not been solved for the 10nm generation. Tool readiness doesn’t seem to be the issue. It’s mostly device physics.

And has he then points out, it's a tall set of requirements and the decision for 7nm hasn't/hadn't been made yet.

I gotta say though, that what he says about High-k doesn't really line-up with "The High-k Solution" article. Okay, high-k might have been ready, but it wasn't really delayed since it was simply planned to go along the metal gates at the 45nm node.

So interesting information that does lower my confidence in III-V at 10nm, even though the vast majority of the data points point to it.

Edit: The bold part for TLDR:

http://forums.anandtech.com/showpost.php?p=34198524&postcount=1. Maybe they have other interesting, even secret, stuff planned for 10nm, though.