DrMrLordX

Lifer

- Apr 27, 2000

- 23,233

- 13,324

- 136

~5-15% performance uplift

Wait, what? Even the leaked slide for 8+16 Arrow Lake (node not indicated) was saying +~20% vs. Raptor Lake @ 250W PL2. Unless I read it wrong?

~5-15% performance uplift

20A is for mobile and client is N3That isn’t what Intel says. Intel is using Intel 20a, which is a 2nm class node. I know that some here have indicated they are dual sourcing for compute chiplets, however they’ve all but denied this.

The power limit reduction is in line with Intel 20a. Notice that Intel (according to the earlier rumor) dropped their power limits just enough to be in line with AM5 parts.

Regardless of process, It is beginning to become clear what Arrow Lake is (I already suspected something like this was going on, glad to see I wasn’t wrong)

~5-15% performance uplift, 40%+ power reduction (huge perf/watt improvement)

Intel won’t get all the credit they deserve. They are fixing their perf/watt issues. Bravo. I look forward to further details.

How dare they not have Nova Lake backported to Intel 7++++? <<< The question I would demand to know the answer to if I were an Intel investor.They could do Raptor Lake Refresh Refresh.

Hmmm...That isn’t what Intel says.

Haven't seen a single leaker deny it. Not a single source. Not RGT, not MLID, not Adroc, not Exist50, literally not a soul.I know that some here have indicated they are dual sourcing for compute chiplets

That's just so much cap.however they’ve all but denied this.

Also in line with N3..The power limit reduction is in line with Intel 20a. Notice that Intel (according to the earlier rumor) dropped their power limits just enough to be in line with AM5 parts.

When are you going to put on your big boy pants and start contributing to any threads? I swear three fourths your comments are just meme-ing on Intel... even on AMD threads lmaoWhen is Intel gonna put on their big boy pants and start making CPUs like they used to (Dothan/Nehalem/Haswell)?

Zen 2-5 doesn't count because AMD is using chiplets with trash packaging and high latency. What a crutch.Alder Lake doesn't count coz it's using the e-cores cluster as a crutch.

Me no engineer.When are you going to put on your big boy pants and start contributing to any threads?

How do you know it's trash? Is AMD using something better for server/TR and if so, does the better packaging translate to real world performance gains?Zen 2-5 doesn't count because AMD is using chiplets with trash packaging and high latency. What a crutch.

Mega chonk L3 cache, can't wait for latency results lol.

I would say Conroe, Nehalem and Haswell. As for Big/Small, it's already a chosen path for summer access and there's no quick application to move away from it.When is Intel gonna put on their big boy pants and start making CPUs like they used to (Dothan/Nehalem/Haswell)? Alder Lake doesn't count coz it's using the e-cores cluster as a crutch.

I would say Conroe, Nehalem and Haswell.

The best thing would be compilers optimizing the application codepaths so that the most performance sensitive functions/threads are executed on the P-cores. The E-cores are fine for background tasks or anything that you just leave running and may check back in a few minutes or even hours coz it's not that urgent.The point is moving forward as more and more applications become increasingly multithreaded the hybrid approach will make more and more sense.

Why would the best thing be the complier doing it? The best thing is the programmer doing it. The programmer knows better than anyone if it is a time-critical thread or not.The best thing would be compilers optimizing the application codepaths so that the most performance sensitive functions/threads are executed on the P-cores.

It would be less cumbersome if the compiler were to do it. It is feasible to design a compiler that understands how long certain instruction mixes will take to execute so put those on the P-cores. For the programmer to do that, a lot of experience is required and it won't solve anything because companies don't always hire the best and brightest.Why would the best thing be the complier doing it? The best thing is the programmer doing it. The programmer knows better than anyone if it is a time-critical thread or not.

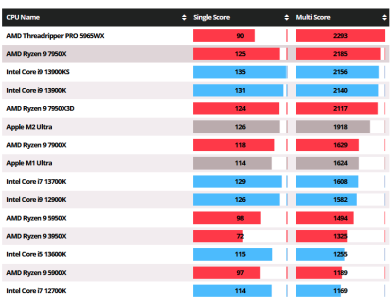

"Leading" by 2.1% in multi while intel is "leading" by 4.8% in ST (comparing to 13900K, not KS). Come on man, performance is pretty much a wash.The best thing would be compilers optimizing the application codepaths so that the most performance sensitive functions/threads are executed on the P-cores. The E-cores are fine for background tasks or anything that you just leave running and may check back in a few minutes or even hours coz it's not that urgent.

Cinebench 2024 Scores [CPU & GPU] (Updated Results)

The new Version of Cinebench, 2024, benchmarks CPUs and GPUs in the popular Redshift render engine. We benchmarked all modern CPUs and GPUs and list them in our score overview.www.cgdirector.com

View attachment 86870

7950X is leading in MT score and that's at lower power consumption. Intel has a long way to go before they can exceed let alone match Zen's perf/watt.

Yes you are right. But I don't know why you quoted me? As I wrote above AMD has a process advantage over Intel. Their lead would even be larger in MT if they used a hybrid approach. AMD has that card in their back pocket when they need to pull it.The best thing would be compilers optimizing the application codepaths so that the most performance sensitive functions/threads are executed on the P-cores. The E-cores are fine for background tasks or anything that you just leave running and may check back in a few minutes or even hours coz it's not that urgent.

Cinebench 2024 Scores [CPU & GPU] (Updated Results)

The new Version of Cinebench, 2024, benchmarks CPUs and GPUs in the popular Redshift render engine. We benchmarked all modern CPUs and GPUs and list them in our score overview.www.cgdirector.com

View attachment 86870

7950X is leading in MT score and that's at lower power consumption. Intel has a long way to go before they can exceed let alone match Zen's perf/watt.

Compilers can potentially tell what takes a long time to execute and what can be executed quickly. But, they probably do not know importance of the tasks without programmer knowledge. Easiest example that I can think of is a background virus scan of the whole computer. That might take hours to do. Should the compiler thus put it as a priority on a P core? Or course not. That background scan should run on an E core. ANY programmer would know that.It would be less cumbersome if the compiler were to do it. It is feasible to design a compiler that understands how long certain instruction mixes will take to execute so put those on the P-cores. For the programmer to do that, a lot of experience is required and it won't solve anything because companies don't always hire the best and brightest.

Besides, the number of programmers that are able to analyze code performance and optimize it, makes up a really small percentage of the total programmer population of the world. It's hard enough to teach people to code. Optimizing code is a dark art and very few are able to get there. Better compilers are the solution.

At the cost of much higher power draw in all core workloads.Come on man, performance is pretty much a wash.

I agree with your hybrid approach thoughts. However, until and unless AMD jumps in with their implementation, we won't know how good it can really be. Intel is just working in a panicky damage control mode. Their main objective is not to lose face in the public eye. They could also change their tactics abruptly if they manage to come out with a highly performant and small core and then ditch hybrid or put 4 E-cores in the SoC tile and call it a day.Yes you are right. But I don't know why you quoted me?

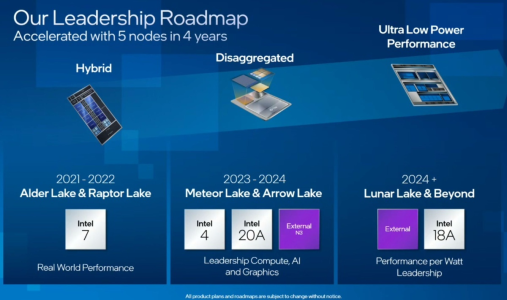

Uh, you do understand that even on Meteor Lake, TSMC is used for graphics, etc, right? Meteor Lake is not dual sourced, yet it is listed right there next to arrow lake. This slide (and variants of it) keep getting brought up, but I strongly suspect you folks are taking it out of context.Hmmm...

View attachment 86864

Haven't seen a single leaker deny it. Not a single source. Not RGT, not MLID, not Adroc, not Exist50, literally not a soul.

That's just so much cap.

Also in line with N3..

MTL is listed right under Intel 4. ARL is listed under "external N3" and "Intel 20A". Notice how the block specifically says "external N3" not just "External". We know MTL uses no N3 tiles, so hence it has to be for ARL. And we know they are only talking about compute tiles, else they would list "external N5" for the GPU tile in MTL.Uh, you do understand that even on Meteor Lake, TSMC is used for graphics, etc, right? Meteor Lake is not dual sourced, yet it is listed right there next to arrow lake. This slide (and variants of it) keep getting brought up, but I strongly suspect you folks are taking it out of context.

However, I am done having this argument. I have said my piece. We will see how things play out.

Perhaps ARL-R will fix a lot with 300-400mhz higher clocks. I also don’t think Zen 5 is going to bring some crazy 1T perf increase.You know, looking at all the recent talk about Intel's next couple CPU generations, one has to wonder how Intel is supposed to compete with Zen 6 in 2025 with PTL and ARL-R, both which appear to be esentially LNC based. MT I'm guessing is not really a problem (since Intel looks like they can just spam the cinememe cores lol) but based on AMD's historical cadence, would Zen 6 not be esentially a full to half generation ahead in single core performance?

Even a ~20% increase in ST perf, which shouldn't be crazy at all, would bring parity between Zen 5 and ARL. I struggle to see how a small percentage increase in clocks could help overcome the likely 10-20% increase in ST performance Zen 6 is likely going to bring. Not to mention thePerhaps ARL-R will fix a lot with 300-400mhz higher clocks. I also don’t think Zen 5 is going to bring some crazy 1T perf increase.