heh, that reminded me to create a mastadon account.davidbepo (@davidbepo@mastodon.social)

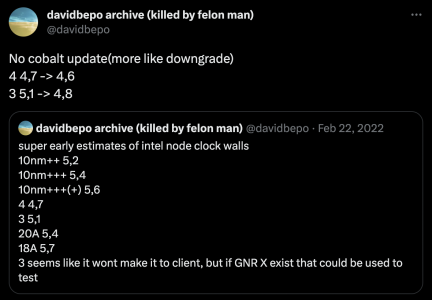

aside from losing well, WELL over 20% in perf this also means ARL gets a node downgrade compared to MTL, its predecessor, which already failed to reach 5 GHz, ARL should regress clocks even further and while i expect IPC here to be better than AMD the massive clock gap and SMT L should mean Zen5...mastodon.social

Oh man, I figured he would be and sure enough. Bepo is having a meltdown lmao.

I'm a bit confused about SMT though. I believe that LNC isn't gonna have SMT, but Bepo is claiming LNC has SMT available but won't be used bcuz of bugs? Idk. The difference here between the two scenarios (LNL not having SMT in the first place vs LNL having SMT but not enabling it due to bugs) is pretty big IMO, even if to the end user it's not.

Something else Bepo claimed was that E-cores in LNL were placed off ring. Ik he was hating on the decision, but is this not actually beneficial for what LNL looks like it's going to be? It won't have to share that voltage plane as the P cores, and I'm assuming the E-cores will be able to be used as the "LP" E-cores are being used in MTL SOC tile.

Also the 20A shilling is insane lol. Why does he hate N3E so much?

I'm also half convinced Bepo is trying to reverse jinx Intel or something haha

fr. It's not the best look, but ARL looks to have been planned to dual source for a while, and IMO it's not that big of a deal. GNR is the real deal tho, Intel has no excuses if GNR/SRF ends up behind schedule.Still extremely disappointing honestly, would literally have rather seen them do ARL on i3 and actually ship a load of volume, but oh well.