So we've discussed Lunar Lake being on N3.

But more interestingly and I think only lightly touched here is that

apparently the entirety of Arrow Lake - including mobile - will now be N3 only.

Second link, explicitly claiming 20A ARL tile is canned.

@H433x0n recall our conversation on Intel claiming "manufacturing ready" and the importance of that whole "actually yielding quality silicon

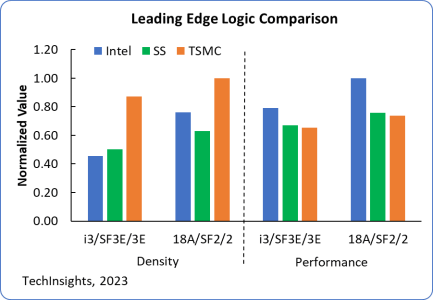

with high volume" thing? Keep in mind this isn't even a particularly high bar, it's nothing like the kind of quality yields, volume and dice TSMC usually pumps in that first year for Apple. So now we're quite possibly if not likely looking at not only no client DGPUs or iGPU tiles on i4/i3/20A, and now no ARL

at all - not just mobile - on 20A.

You have to read between the lines, paper nodes being available don't mean

anything particularly where we know recent results have been poor and clients are few and far. The entire point of a foundry is, you know, the whole revenue thing via mass market silicon, true even internally. It's not an 8th grade science fair. Also again highlights how PowerVIA and Backside Power Delivery alone doesn't mean anything - even LNL on N3 highlights that and should make you question your previous opinion on 20A and 18A.

I won't claim this is definitive proof - it's a rumor, but I am not inclined to reflexively doubt this rumor having followed the sources and knowing the existing rumors and the directions they point to. This is just a step further.

Will be interesting to see where their server parts go, and also when (God forbid it gets to "if" but I don't think so...) we'll get an Intel client product on IFS' i4 or newer nodes, save for MTL. Frankly, Intel 3 having HD cells means I'd love to see them do something lower cost, lower power with that, even an MTL refresher of some kind, but they won't.

Mind you, I don't like seeing this. Would rather just be wrong.