nicalandia

Diamond Member

OpenVino is the Absolute best case scenario to display Intel's new AMX SIMD

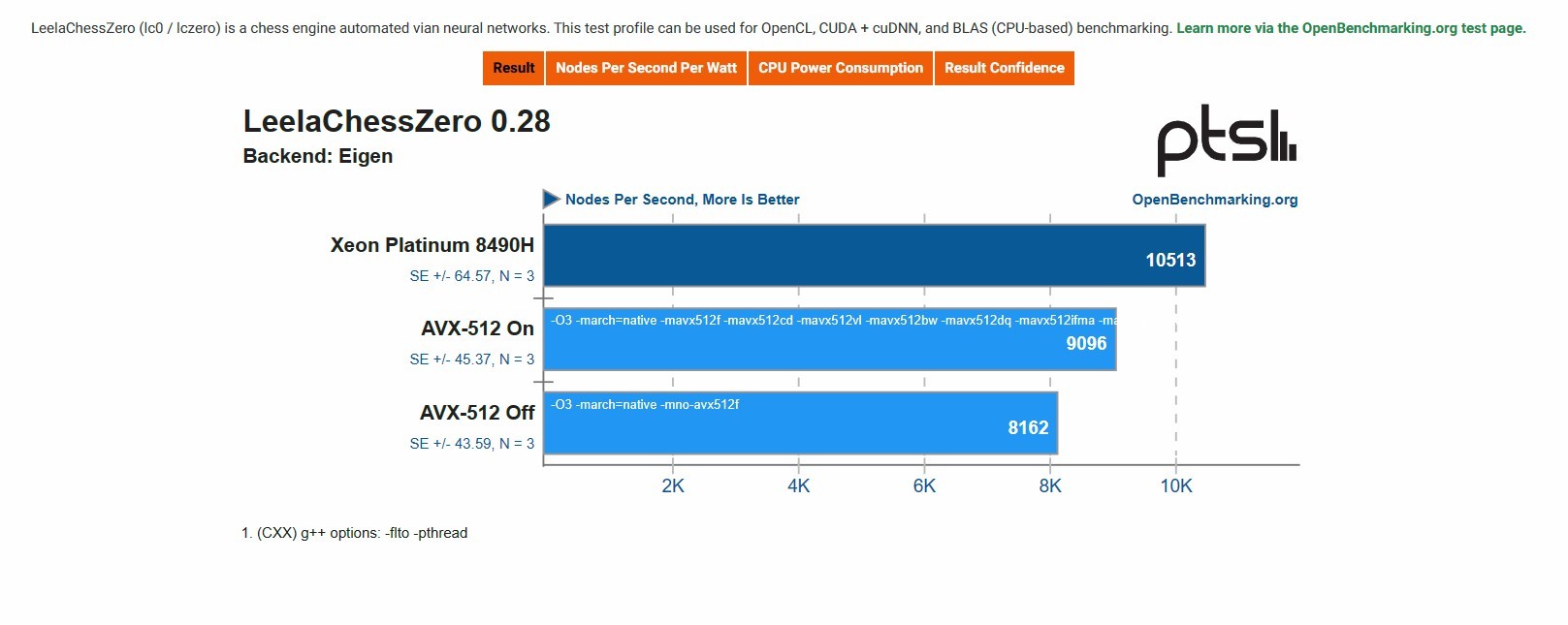

I was able to make a comparison between AMD 2S 9654 With AVX-512 Enabled and Disabled and made a comparison with Intel 2S 8490H In OpenVINO which takes advantage of AVX2/AVX-512 and now AMX.

The Gains with AMX are in some instances absurd like this chart

But the Geomean brings it about 36% Higher

Also the AVX-512 Performance of Genoa is Also Amazing

This is the Link of the performance Comparison.

AMD Genoa AVX-512 ON/OFF vs Intel SPR-SP AMX

Its good that AMD was able to add AVX-512 Otherwise the performance difference on OpenVINO would have looked rather Silly.

I was able to make a comparison between AMD 2S 9654 With AVX-512 Enabled and Disabled and made a comparison with Intel 2S 8490H In OpenVINO which takes advantage of AVX2/AVX-512 and now AMX.

The Gains with AMX are in some instances absurd like this chart

But the Geomean brings it about 36% Higher

Also the AVX-512 Performance of Genoa is Also Amazing

This is the Link of the performance Comparison.

AMD Genoa AVX-512 ON/OFF vs Intel SPR-SP AMX

Its good that AMD was able to add AVX-512 Otherwise the performance difference on OpenVINO would have looked rather Silly.

Last edited: