nicalandia

Diamond Member

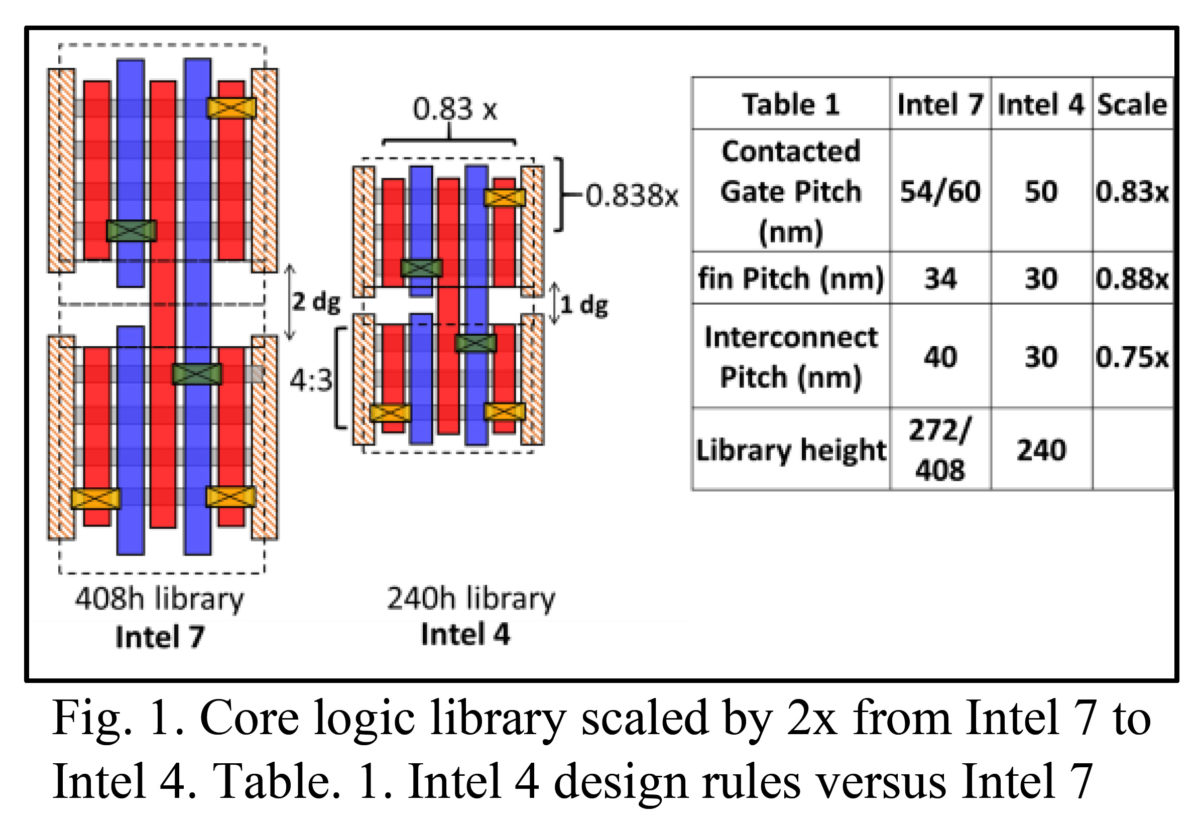

And 1.63x would be the best case scenario, caches and PHYs scale worse so sounds like they won't hit 50% more transistors per mm^2 on any real designs.

The Area reduction is only 25% on the compute side(Compute Tile vs Compute section: Alder Lake vs Meteor Lake)

Intel 7

8P Core cluster: 84.23 mm^2

8E Core cluster: 26.34 mm^2

Intel 4

8P Core cluster: 62.9 mm^2

8E Core cluster: 19.8 mm^2

Last edited: