-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Intel current and future Lakes & Rapids thread

Page 637 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

DrMrLordX

Lifer

Is RPL PL2 going to be the same as ADL?

If so how much do you think performance/watt will increase in MT?

Allegedly Raptor Lake's top SKU will have the same ~250W PL2 value. It'll have two 8c Gracemont clusters at an unknown clockspeed with extra L2, and if on a newer motherboard (e.g. not z690) it'll have a separate voltage rail available for Gracemont so it won't have to pull the same volts as the Raptor Cove cores. That should improve perf/watt in MT workloads assuming Intel's boost maps for those workloads allows the Gracemont clusters to run at lower clocks and volts than Alder Lake. The 12900k has its 8c Gracemont cluster running at the same voltage as the Golden Cove cluster, and forces clocks to 3.9 GHz which is well out of the efficiency range for Gracemont.

To put a finer point on it, if in full MT scenarios a 13900k can run its 16c Gracemont @ 3.2 GHz with some lower voltage than what is used on Alder Lake's 3.9 GHz 8c Gracemont cluster, you'll see increased throughput without that much extra power draw.

Where did that come from? Pretty sure DLVR (which should be like FIVR in that it shifts the voltage regulation onto the die) is a mobile-only feature. At least for Raptor Lake. It'd probably break motherboard compatibility if they added it for desktop.and if on a newer motherboard (e.g. not z690) it'll have a separate voltage rail available for Gracemont so it won't have to pull the same volts as the Raptor Cove cores

DrMrLordX

Lifer

Where did that come from? Pretty sure DLVR (which should be like FIVR in that it shifts the voltage regulation onto the die) is a mobile-only feature. At least for Raptor Lake. It'd probably break motherboard compatibility if they added it for desktop.

I haven't seen if it's mobile-only or not. Whether it breaks compatibility with Z690 remains to be seen. If that feature is only on mobile then lol woops. Too bad for Raptor Lake-S.

edit: reports like this (from Reddit) seem to indicate it could be a desktop feature?

Intel Raptor Lake CPUs To Feature Digital Linear Voltage Regulator 'DLVR' - Could Help Reduce Power Consumption By 25%

Intel's 13th Gen Raptor Lake CPUs are going to feature new DLVR technology to help reduce power consumption and temperatures.

Most likely mobile only: https://cdn.videocardz.com/1/2021/11/Intel-Raptor-Lake-DLVR.jpg

Intel already has FIVR on Alder Lake:

Plenty of voltages are generated by FIVRs from VCCInAux. As You can see E-Core L2's are fed by FIVR currently and most likely it was supposed to feed E-Cores as well. But marketing morons asked for 4Ghz clocks for E-Cores that are beyond their efficiency curve and results in too much power draw for FIVR to handle, so they routed them to VccIA instead.

So Intel is free to fix this on 600 series motherboards as this is internal to CPU thing, just maybe BIOS option to control this voltage needs to be added ( like VccSA etc are controlled today, that control FIVC, not voltage rail of MB ).

Plenty of voltages are generated by FIVRs from VCCInAux. As You can see E-Core L2's are fed by FIVR currently and most likely it was supposed to feed E-Cores as well. But marketing morons asked for 4Ghz clocks for E-Cores that are beyond their efficiency curve and results in too much power draw for FIVR to handle, so they routed them to VccIA instead.

So Intel is free to fix this on 600 series motherboards as this is internal to CPU thing, just maybe BIOS option to control this voltage needs to be added ( like VccSA etc are controlled today, that control FIVC, not voltage rail of MB ).

IntelUser2000

Elite Member

ARM + Android and ARM + iOS have been doing it for years.

Mobile devices have a far, far easier time because,

1) Locked and running on a standard account rather than admin which limits adjusting system settings.

2) Apps are pretty much all from the Store, which has some standards and is all very controlled.

3) Multitasking capability is much less capable compared to Windows.

Power management, and scheduling is far easier than on Windows because of that. On Windows if you have 10 windows open, they all run, all the time. Try sleeping your cores in between, or deciding where to allocate the cores.

Or applications that can be written by anyone. Yes few applications from top developers may consider all that in mind, but even they don't.

Last edited:

IntelUser2000

Elite Member

"It's late in 2013. Intel is frantic about losing the mobile CPU wars to ARM. Meetings with all the validation groups. Head honcho in charge of Validation says something to the effect of: "We need to move faster. Validation at Intel is taking much longer than it does for our competition. We need to do whatever we can to reduce those times... we can't live forever in the shadow of the early 90's FDIV bug, we need to move on. Our competition is moving much faster than we are" - I'm paraphrasing. Many of the engineers in the room could remember the FDIV bug and the ensuing problems caused for Intel 20 years prior. Many of us were aghast that someone highly placed would suggest we needed to cut corners in validation - that wasn't explicitly said, of course, but that was the implicit message. That meeting there in late 2013 signaled a sea change at Intel to many of us who were there. And it didn't seem like it was going to be a good kind of sea change. Some of us chose to get out while the getting was good. As someone who worked in an Intel Validation group for SOCs until mid-2014 or so I can tell you, yes, you will see more CPU bugs from Intel than you have in the past from the post-FDIV-bug era until recently."

The mistake there was cutting corners rather than addressing the core issue of why they were taking so long.

Remember the articles about how Jim Keller went in there and changed the way they looked at CPU design and how work was allocated? Something like that.

If you are doing it the wrong way, then do it the right way. There were probably weird way of doing things and whole bunch of bureaucratic processes they had to go through and why it was taking so long.

moinmoin

Diamond Member

I guess bullheaded Intel had to learn it the hard way. And going by the high amount of steppings it doesn't seem to be quite there yet.The mistake there was cutting corners rather than addressing the core issue of why they were taking so long.

Remember the articles about how Jim Keller went in there and changed the way they looked at CPU design and how work was allocated? Something like that.

If you are doing it the wrong way, then do it the right way. There were probably weird way of doing things and whole bunch of bureaucratic processes they had to go through and why it was taking so long.

Intel already has FIVR on Alder Lake:

View attachment 62342

Plenty of voltages are generated by FIVRs from VCCInAux.

Not for the IA cores unfortunately. It's a hardware limitation. If this is related to DLVR and they can fix it for Raptor Lake mobile we likely won't see a fix for Raptor Lake desktop. This is unfortunate but mobile is much more important when it comes to efficiency.

nicalandia

Diamond Member

DrMrLordX

Lifer

1) Locked and running on a standard account rather than admin which limits adjusting system settings.

I mean I guess? You can run a default Win11 install on Alder Lake and it's not like it improves performance or scheduling. It still does goofy stuff like shunting a CPU-intensive workload to the e-cores if you switch context between applictions, which is something Android does not seem to do.

2) Apps are pretty much all from the Store, which has some standards and is all very controlled.

Google Play is pretty relaxed. Obvious power viruses or other semi-malicious applications might not get on the store, but honestly you can sling software of dubious quality there if you like. I haven't looked at design recommendations for Android recently, but the last time I did there were already octal core CPUs out there with funky tri-cluster arrangements, and there wasn't much in the way of developer recommendations for thread scheduling (that I recall).

3) Multitasking capability is much less capable compared to Windows.

The last two phones I've had have had no problems keeping multiple applications running simultaneously. It hasn't been anything too-intensive, though, and I wasn't monitoring core usage. Might be interesting to load up GB5 on my phone and try running other stuff at the same time, to see what happens.

uzzi38

Platinum Member

From my understanding the LGA1200 motherboards and socket specification just doesn't have the capabilities to handle another voltage plane so yeah, this.Where did that come from? Pretty sure DLVR (which should be like FIVR in that it shifts the voltage regulation onto the die) is a mobile-only feature. At least for Raptor Lake. It'd probably break motherboard compatibility if they added it for desktop.

ashFTW

Senior member

Did you mean LGA1700?From my understanding the LGA1200 motherboards and socket specification just doesn't have the capabilities to handle another voltage plane so yeah, this.

uzzi38

Platinum Member

Yes I didDid you mean LGA1700?

nicalandia

Diamond Member

Saylick

Diamond Member

Not sure if this is the place to put it, but Intel's ISC 2022 announcements are pretty impressive (if they can deliver on time). The idea of a heterogenous HPC product in a single package appears to be the direction of both Intel (XPU) and AMD (APU). We'll just see who gets there first.

AnandTech Forums: Technology, Hardware, Software, and Deals

Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

www.anandtech.com

IntelUser2000

Elite Member

Rialto Bridge looks a bit underwhelming based on "30% increased application performance", but I guess that depends on how good Ponte Vecchio is.

Also, Meteorlake-S in Q1 2024 and Arrowlake-S in the same year. See what I mean by most Meteorlake chips way later than middle of 2023?

Also, Meteorlake-S in Q1 2024 and Arrowlake-S in the same year. See what I mean by most Meteorlake chips way later than middle of 2023?

Henry swagger

Senior member

I think its on desktop too because raptor lake single core is 5.8ghz and all core 5.5ghz.. they need dlvr to reduce watts if they hit 300watt ppt to maybe 240pptI haven't seen if it's mobile-only or not. Whether it breaks compatibility with Z690 remains to be seen. If that feature is only on mobile then lol woops. Too bad for Raptor Lake-S.

edit: reports like this (from Reddit) seem to indicate it could be a desktop feature?

Intel Raptor Lake CPUs To Feature Digital Linear Voltage Regulator 'DLVR' - Could Help Reduce Power Consumption By 25%

Intel's 13th Gen Raptor Lake CPUs are going to feature new DLVR technology to help reduce power consumption and temperatures.wccftech.com

IntelUser2000

Elite Member

I think its on desktop too because raptor lake single core is 5.8ghz and all core 5.5ghz.. they need dlvr to reduce watts if they hit 300watt ppt to maybe 240ppt

DLVR only benefits up to 70A and after 50A, the benefit drops rapidly. So that's maximum slightly under 100W, likely under 70W.

That's why early leaked roadmaps had DLVR only for mobile platform. Desktop chips will get better perf/watt because of the extra 8 E cores and iterative improvements that always happen.

Power isn't going down on Raptorlake. They'll use all the extra perf/watt for better performance.

Way I heard things, Keller didn't have time to really succeed with the SoC design teams, but something changed with Core in particular (Atom being on the right path already). But the implication I got was less "willingly reformed" and more "threatened with obsolescence". Actually, I heard they kinda rebuffed him at first.Remember the articles about how Jim Keller went in there and changed the way they looked at CPU design and how work was allocated? Something like that.

Where did you see Q1 for MTL-S?Also, Meteorlake-S in Q1 2024 and Arrowlake-S in the same year. See what I mean by most Meteorlake chips way later than middle of 2023?

I might be wrong on this, but my understanding of DLVR was more as a FIVR alternative? replacement? Some of thing of the sort. This patent is kinda confusing in that regard, but maybe just a different use for the same tech? Wonder also how multiple DLVR would scale... Anyway, still don't really expect it for desktop, but maybe?DLVR only benefits up to 70A and after 50A, the benefit drops rapidly. So that's maximum slightly under 100W, likely under 70W.

Last edited:

Shortening the paths between CPU/GPU/memory is the thing. So nVidia, AMD, and Intel are going that way. For AMD it should be MI300 since it can operate in "an APU mode". So next gen.Not sure if this is the place to put it, but Intel's ISC 2022 announcements are pretty impressive (if they can deliver on time). The idea of a heterogenous HPC product in a single package appears to be the direction of both Intel (XPU) and AMD (APU). We'll just see who gets there first.

DrMrLordX

Lifer

The way they have Sapphire Rapids and Emerald Rapids laid out on that slide is weird. They show "4th Gen Xeon" where bog-standard Sapphire Rapids should be, and then they don't show an HBM-equipped Emerald rapids as the successor to HBM-equipped Sapphire Rapids. Wut?

Also kind of hard to get excited about Rialto Bridge with Ponte Vecchio being the way it is.

And no Habana product past 2023?

Also kind of hard to get excited about Rialto Bridge with Ponte Vecchio being the way it is.

And no Habana product past 2023?

nicalandia

Diamond Member

The way they have Sapphire Rapids and Emerald Rapids laid out on that slide is weird. They show "4th Gen Xeon" where bog-standard Sapphire Rapids should be, and then they don't show an HBM-equipped Emerald rapids as the successor to HBM-equipped Sapphire Rapids. Wut?

Also kind of hard to get excited about Rialto Bridge with Ponte Vecchio being the way it is.

And no Habana product past 2023?

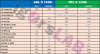

Hey Look at this, the one on the Left is without HBM Memory and the one with the right it's with HBM

Last edited:

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-