I can see Intel coming or attempting to come back with whatever they decide to release after Alderlake for HEDT. Intel can't be cheap with core counts and can't charge as high as AMD can to win people back. Don't you just love competition?!nah watch knowing intel... the consumer line will be big / little the HEDT will be Big/Gigantic

They need to spice it up a bit to fight ThreadRipper.

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Discussion Intel current and future Lakes & Rapids thread

Page 480 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

44 lanes with RKL, right? Would not surprise me one bit if Intel designed Alderlake with far more in mind, especially with PCIE5 devices (mainly storage) right around the corner. Though I suspect the PCIE5 era will be as short lived as the PCIE4 era. Marvell announced the first pcie5 controller a while back, and there's some rumor that a few companies have began work on pcie6 controllers. Direct Storage tech is going to be a huge whopper.Did anyone hear of a pci-e lane count on Alder Lake?

I am wondering since its technically 2 silicon, does that mean double the pci-e lanes?

IntelUser2000

Elite Member

30% boost from Hyperthreading is only in the very best case scenario.

Yes, but we're talking Cinebench, where it does get 30% benefit.

And Hyperthreading works well in most scenarios where it has lot of thread level parallelism. So in most cases where it doesn't work well with HT, extra cores using Gracemont won't help either.

It's just a matter of simple numbers. Hardware scheduling isn't magic.

Did anyone hear of a pci-e lane count on Alder Lake?

I am wondering since its technically 2 silicon, does that mean double the pci-e lanes?

Excuse me, but how is it two silicon? Are you saying Alderlake is an MCM? No, it has two very different cores but that's not at all connected to PCI-e lanes. PCI-e lanes are entirely on their own.

Alderlake has 48 lanes by the way.

Excuse me, but how is it two silicon? Are you saying Alderlake is an MCM? No, it has two very different cores but that's not at all connected to PCI-e lanes. PCI-e lanes are entirely on their own.

Alderlake has 48 lanes by the way.

From my understanding, its a band aide of atom core and a regular core, kinda like how ARM is with big and little cores, but way more complex.

So it has 2 independent computes of completely different category.

PCI-E lanes are on both board and cpu.

From my understanding the CPU PCI-E lanes are physicals bridges which branch from the CPU.

So i was theorizing, if they are meshing a desktop and an atom cpu in 1 package, maybe they will give us the physical lanes from both which are on the cpu.

And is 48 lanes confirmed for the consumer? or is this still rumor?

Last edited:

From my understanding, its a band aide of atom core and a regular core, kinda like how ARM is with big and little cores, but way more complex.

So it has 2 independent computes of completely different category.

PCI-E lanes are on both board and cpu.

From my understanding the CPU PCI-E lanes are physicals bridges which branch from the CPU.

So i was theorizing, if they are meshing a desktop and an atom cpu in 1 package, maybe they will give us the physical lanes from both which are on the cpu.

And is 48 lanes confirmed for the consumer? or is this still rumor?

"CPU" lanes don't actually have anything to do with the CPU cores themselves. It's just shorthand for "lanes on the same die as the CPU". Hybrid doesn't affect their count or behavior in any way.

Your math is also off IF ADL-S can hold 5GHz all core on the bigger cores. It's no longer 1.2x if that's the case.You forgot two very important points, frequency and Hyperthreading.

Hyperthreading is responsible for 30% performance gain. Also current desktop CPUs clock 20-30% faster than Gracemont will.

Then you get 8x1.2 + (8x*0.85/1.3/1.2) = 14

This also assumes yet another large caveat: Hybrid will work without any overhead.

Simple arithmetic also don't take into account how the current cores perform. 6000 for Rocketlake, and 925 for 10W Tremont.

Your simple calculation results in 7200 for Golden Cove and 4800 for Gracemont. My calculation says 7200 for Golden Cove and nearly 3300 for Gracemont.

3300 seems like a big stretch to me nevermind 4800.

coercitiv

Diamond Member

The entire 2X performance over previous gen calculation was done by ignoring power estimates for the time being. As of right now we don't know if 10ESF will be enough to fully offset the higher power usage of the two clusters or whether the big cluster will need to clock bellow RKL when power limited, which means that using power limited scenarios, while possibly advantageous for ADL-S, will only introduce another unknown variable in the equation. Everybody's using the (all-core) turbo clocks to estimate the maximum potential of the chips.Your math is also off IF ADL-S can hold 5GHz all core on the bigger cores. It's no longer 1.2x if that's the case.

PS: also @IntelUser2000 was conservative with the 1.2X multi, since 5/3.7 -> 1.35X, meaning he already factored in a safety cushion for clock delta between clusters.

Last edited:

IntelUser2000

Elite Member

@Zucker2k 1.2x for is based on the Intel leak about Alderlake.

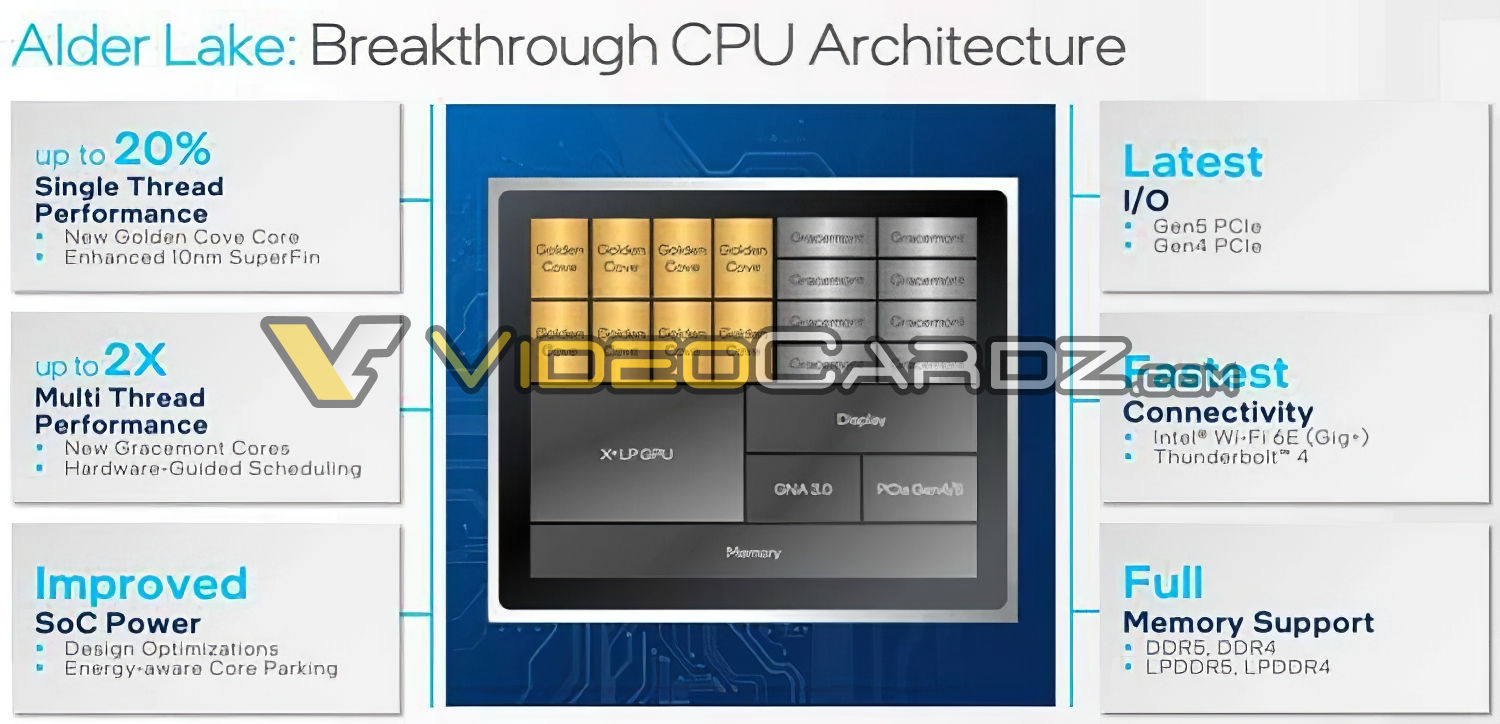

And by the way it said "up to 20% better single threaded performance". It also said 2x multi and while I can see it for up to 28W parts it's hard to see how the desktop version would be 2x of Rocketlake.

So we can't believe anything Intel says nowadays since they completely failed in execution, but when Intel leaks about Alderlake comes out somehow we're expecting it to be way beyond what it says?

And by the way it said "up to 20% better single threaded performance". It also said 2x multi and while I can see it for up to 28W parts it's hard to see how the desktop version would be 2x of Rocketlake.

So we can't believe anything Intel says nowadays since they completely failed in execution, but when Intel leaks about Alderlake comes out somehow we're expecting it to be way beyond what it says?

DrMrLordX

Lifer

Brian Krzanich supposedly gave Murthy the final sign off on their 2015 ACT layoffs which fired 12k people

Hmm!

Intel discriminated against eight older workers in 2015 layoffs, EEOC finds

The commission’s finding follows a five-year investigation triggered by employee complaints, which cited investigations by The Oregonian into Intel’s layoff practices.

Murthy was responsible for most of that? Ouch.

dullard

Elite Member

Note: All my comments were about Alder Lake in general and not Cinebench.Yes, but we're talking Cinebench, where it does get 30% benefit.

And Hyperthreading works well in most scenarios where it has lot of thread level parallelism. So in most cases where it doesn't work well with HT, extra cores using Gracemont won't help either.

Raichu claims the 12900K gets more than 810 in R20 ST and 11k in MT. Not overclocking but is using water.

That would be close to 30% faster than 11900K in ST. I still wonder about AVX acceleration. Or maybe vector performance in general has just gotten a huge boost in both big and small but would it translate to games.

Last edited:

Raichu claims the 12900K gets more than 810 in R20 ST and 11k in MT. Not overclocking but is using water.

That would be close to 30% faster than 11900K in ST. I still wonder about AVX acceleration. Or maybe vector performance in general has just gotten a huge boost in both big and small but would it translate to games.

I'd say Raichu's tone implies not that much faster in other apps.

And of course this can mean both ways. One word replies are hard 🙂

IntelUser2000

Elite Member

That would be close to 30% faster than 11900K in ST. I still wonder about AVX acceleration. Or maybe vector performance in general has just gotten a huge boost in both big and small but would it translate to games.

Hmm, much more credible now.

If it performs that well, then the large Golden Cove cores based on Sapphire Rapids shot is perhaps justified. That's pretty much 30% gain in ST performance per core.

Cinebench doesn't really care about AVX. It's also relatively branchy and reflects general performance quite well in most cases.

11,600 score equals

-8300 Golden Cove? 5 vs 4.7GHz Rocketlake and 30% architectural gains. That would make up for zero gains on Willow Cove.

That leaves 3,300 for Gracemont. Assuming 2.8GHz for 10W Tremont, that implies a greater than 40% gain in performance per clock. That'll defeat Skylake per clock by 7-10%.

Also, 1030 points in Geekbench using same clocks. Isn't that A78 level? Their Atom team is following the ARM team it seems.

Hmm, much more credible now.

If it performs that well, then the large Golden Cove cores based on Sapphire Rapids shot is perhaps justified. That's pretty much 30% gain in ST performance per core.

Cinebench doesn't really care about AVX. It's also relatively branchy and reflects general performance quite well in most cases.

The other thing I was wondering was DDR5 related performance gains beyond just simply bandwidth.

dullard

Elite Member

@Zucker2k 1.2x for is based on the Intel leak about Alderlake.

And by the way it said "up to 20% better single threaded performance". It also said 2x multi and while I can see it for up to 28W parts it's hard to see how the desktop version would be 2x of Rocketlake.

Zucker2k answered your question though. With power spread out amongst more cores (even if some of the cores are smaller) then each big core has less heat. That means adaptive boost should allow Alder Lake to be at the turbo speed longer and for a greater percentage of the time given the same system cooling power capability.Your math is also off IF ADL-S can hold 5GHz all core on the bigger cores. It's no longer 1.2x if that's the case.

- Suppose that Rocket Lake used the full 251 W PL2 power. Spread amongst 8 cores, that would be 31.3 W each (true, uncore has some power too but I'll ignore that for now).

- Suppose that Alder Lake uses the full 228 W PL2 power in rumors. Give ~5 W each to the 8 small cores, that leaves 188 W spread amongst 8 big cores, or 23.5 W each (again uncore uses some power, but I'll ignore that for now).

20% more IPC rumored * 4% higher frequency rumored * ~3% gain from more adaptive boost => 1.2 * 1.04 * 1.03 = 1.285 x faster.

Last edited:

moinmoin

Diamond Member

LOLNot overclocking but is using water.

Like I said, K parts are going to be allowed to go 200 W or more without an unlock from now on.

moinmoin

Diamond Member

Not calling it overclock is still... Well, let's call it further progress in Intel's very own definition of TDP. 🤷Like I said, K parts are going to be allowed to go 200 W or more without an unlock from now on.

Interesting implication for warranty coverage though. Since it's no longer overclock it's all covered by the standard warranty, isn't it?

The other thing I was wondering was DDR5 related performance gains beyond just simply bandwidth.

Two things that Cinebenches do not care about:

1) Memory bw/latency

2) Inter-core comms latency

Basically each execution thread is given a slice of final render that does not depend on results from other threads, that has a rather small and nice spatial and temporal locality working set, that fits L2 caches. And then code that is full of branches is executed. One that does not really use full backend resources of the core due to all mispredicts and stalls and leaves some 20-30% for hyperthreading to extract.

Heaven for ZEN cpus with strong cores and not so good memory subsystem in earlier gens, even abominations that should have never existed like that Threadripper with some CCDs not connected to memory controllers - they got amazing scaling in Cinebenches and horribad results in say compilation or compression.

I think what is happening with Alder Lake - ST: >810 shows that big core is very strong, and other results are not that good cause it is being tested with "stock" DDR5 4800CL66 with Intel "special" BIOS that hurt performance everywhere else, while Cinebenches are immune to those effects.

810 is wow level of performance, Skylake was 500ish land and was premier cpu from Intel sold just last year.

Like I said, K parts are going to be allowed to go 200 W or more without an unlock from now on.

Not calling it overclock is still... Well, let's call it further progress in Intel's very own definition of TDP. 🤷

Will it automatically sustain that assuming the cooling permits?

coercitiv

Diamond Member

As always it depends on the motherboard VRM and firmware.Will it automatically sustain that assuming the cooling permits?

If the 30% single thread improvement is true then what's up with this picture? "up to 20% single thread performance" Fake or something to mislead the competition?

That's probably an average across multiple apps, or the improvement for SpecINT, an industry benchmark. Some applications will be much higher than 20%. With Zen 3 for instance, the performance increase in games was much higher than the touted 18% uplift in IPC.

dullard

Elite Member

Neither. 20% more IPC (from the image), and slightly faster frequencies, and more time in turbo => 30% faster (in some programs).If the 30% single thread improvement is true then what's up with this picture? "up to 20% single thread performance" Fake or something to mislead the competition?

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-