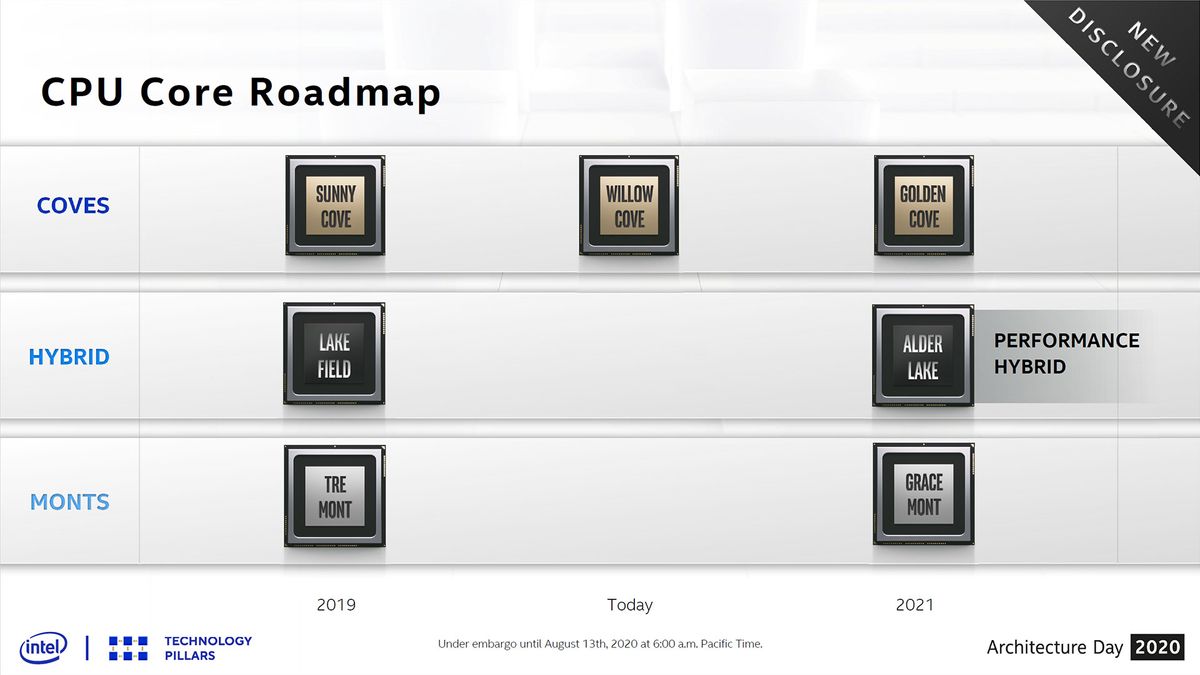

Gracemont also comes with increased vector performance, a nod to an obvious addition of some level of AVX support (

likely AVX2). Meanwhile, the larger Golden Cove cores should support AVX-512.

That split instruction set support could portend optimizations to the hardware-aware scheduler in the operating system, which we'll cover shortly.

...

There's already

plenty of work underway in both Windows and various applications to support that technique via a hardware-guided OS scheduler. Still, the current format for Intel's Lakefield relies upon both cores supporting the same instruction set.

Intel Chief Architect Raja Koduri mentioned that a new "next-generation" hardware-guided OS scheduler that's optimized for performance would debut with Alder Lake, but didn't provide further details.

This next-gen OS scheduler could add in support for targeting cores with specific instruction sets to support a split implementation, but that remains to be seen.