uzzi38

Platinum Member

- Oct 16, 2019

- 2,747

- 6,657

- 146

Not strictly true, Tom's uses 2933 for stock config on intel, at least during the 5600X review

The sites that used same speed RAM also tended to get different results from sites like AT that used the chipsets certified JEDEC settings. The win for Zen 3 *mostly* still there, but it is a lot less clear cut, and in some cases Intel wins.

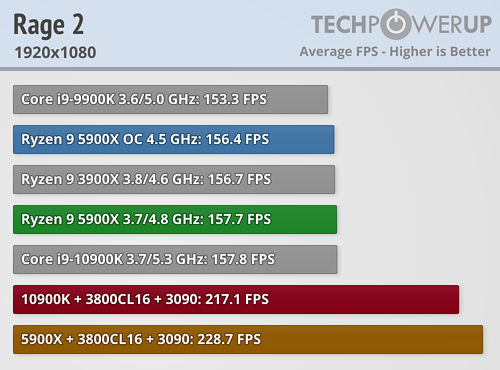

TPU used exactly the same DDR4-3200 RAM settings, using what is a Zen 2 friendly FlareX CL14 kit, and got raked over the coals for it by the AMD crowd when it showed Comet Lake winning in the aggregate with a 2080 Ti.

One has to wonder what would have happened if someone used an Intel friendly RAM kit, stuck that into a Zen 3, and then ran those benchmarks.

Tom's test setup, using 2933 on Intel, 3200 on Zen for stock :

View attachment 36001

Computerbase.de also uses MFR rated RAM speeds :

View attachment 36004

Lol that's not why TPU "got raked over the coals", they acknowledged themselves their results weren't accurate and were a result of what looked like a driver bug between Zen 3 and Turing.

Also, "Zen 2 friendly RAM kit"? It's a memory kit lol, there's no magic AMD favouring or Intel favouring kits.

Btw, Gamer's Nexus use DDR4-3200 for both AMD and Intel and get some of the best results for Zen 3 vs Comet Lake. So much so that an overclocked 10900K (including memory and cache OC) can't match stock Zen 3 results.