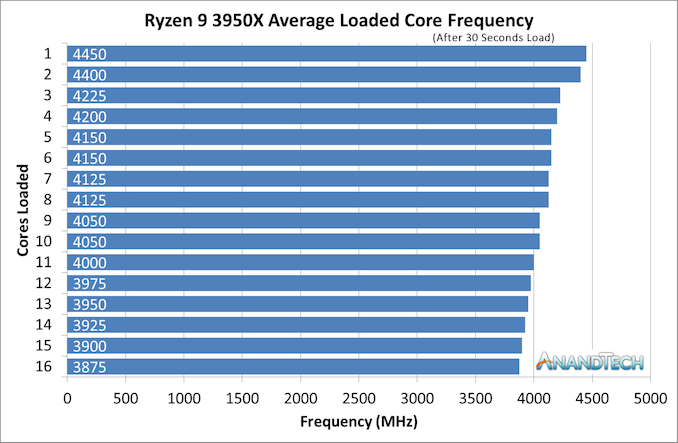

Not really. Average clocks of 3950x are listed

in the anandtech's review. With 16 loaded cores it's almost 3.9 Ghz.

And even when you ignore clock speed (that will realistically give AMD at least a 10% advantage):

- Zen 3 will have at least a 10% IPC lead, realistically more (unless Gracemont is >10% faster than Skylake)

- AMD gains ~40% from SMT in such workloads.

I do agree, that even among MT workloads many do not scale well to 16-24+ threads. Most consumer stuff (outside rendering) will not scale very well past 10-12 cores and should thus run very competitively on Alder Lake. I just find it unlikely that a 8 core Alder lake can beat 16 Zen 3 in workloads that

do scale to 32 threads.

EDIT: Anyway sorry for the OT, won't discuss this point forward.