LightningZ71

Platinum Member

I thought Renoir HS was 35 watts and the regular H parts were 45 watts?

I thought Renoir HS was 35 watts and the regular H parts were 45 watts?

I thought Renoir HS was 35 watts and the regular H parts were 45 watts?

Even funnier will be CML i9 vs RKL i9 in MT loads, although if that segmentation is true then it may actually be good news for RKL performance.OK, this is funny.

Pretty sure it'll fall behind. I'm thinking Intel is just going for the highest ST possible, so that they 'may' jump ahead of Zen3.Even funnier will be CML i9 vs RKL i9 in MT loads, although if that segmentation is true then it may actually be good news for RKL performance.

Even funnier will be CML i9 vs RKL i9 in MT loads, although if that segmentation is true then it may actually be good news for RKL performance.

Isnt that what it is designed for?Let's face it, Comet Lake-S ain't all that. I mean sure it works, it's . . . quite a bit faster than Kabylake and Skylake in MT just from the core count, but Intel should be able to at least match it in MT with 8c Rocket Lake. If they can at least keep the heat flux down to equal the 10900k it won't be a terrible chip. It just will have no real value outside of premium desktop and gaming. That kind of MT performance in 2021 is just not that special anymore.

Yes! Intel knows that enthusiast gamers will shell out for 8fps higher than AMD.Isnt that what it is designed for?

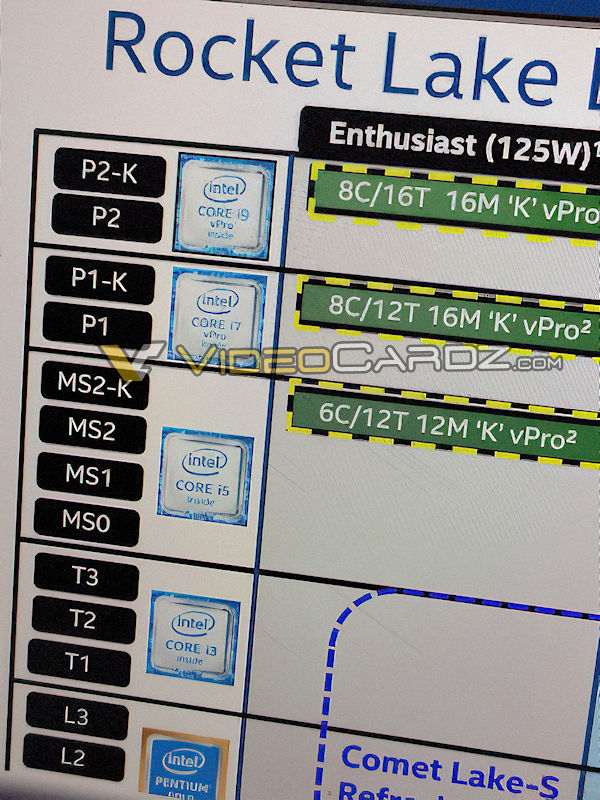

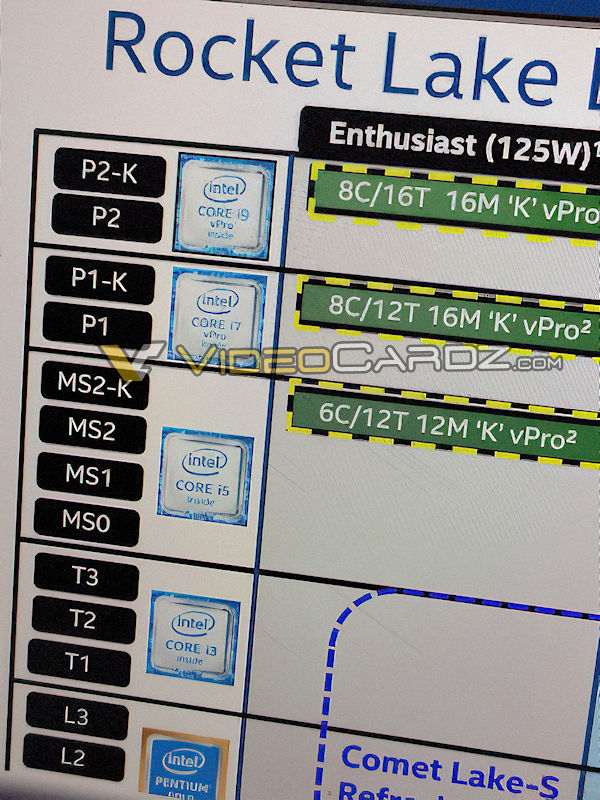

Intel Core i7 vPRO 'Rocket Lake-S' CPUs to get 8 cores and 12 (?!) threads - VideoCardz.com

The next-generation Rocket Lake-S vPRO processors. Intel Core i7 with 12-threads? We received quite an interesting photograph from a reliable source. The picture showcases performance tiers for the upcoming desktop Rocket Lake architecture featuring up to 8 cores and 16 threads. There have been...videocardz.com

OK, this is funny. New rumor saying that the Rocket Lake i7 will be 8C12T. It's probably a typo but it is possible.

IMO the ring bus rocket lake has the standard cache structure, 256KB L2/core

: SiSoftware Official Benchmark Ranker

ranker.sisoftware.co.uk

Rocket Lake S 6C12T model with 256KB L2. Dunno if this means there will be 'Rocket Lake' with Skylake cores as well or there will be models with the L2 cache cut.

IMO the ring bus rocket lake has the standard cache structure, 256KB L2/core

the backport canback portshoot anything IMO

Isnt that what it is designed for?

Can you elaborate? I thought your sentence " It just will have no real value outside of premium desktop and gaming " was the point you were making.

Can you elaborate? I thought your sentence " It just will have no real value outside of premium desktop and gaming " was the point you were making.

I still cannot wrap my head around big.Little for a desktop cpu, well, certainly not for a high performance cpu.Rocket Lake-S will be Intel's non-HEDT desktop flagship until they are able to launch Alder Lake-S

I still cannot wrap my head around big.Little for a desktop cpu, well, certainly not for a high performance cpu.

Rocket Lake-S will be Intel's non-HEDT desktop flagship until they are able to launch Alder Lake-S. It is designed for all computing tasks. Not just gaming. It is also designed to meet the needs of the entire market - DiY, various different OEMs, you name it.

It will be a change for sure, though, and it may not stack up all that well against chips coming out this year, much less those currently scheduled for 2021 . . .

Targeting Alder Lake meanwhile is flipping on MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, FSGSBASE, RDRND, FMA, CLDEMOTE, PTWRITE, WAITPKG and SERIALIZE instruction set support.

Sapphire Rapids enables: MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, PKU, AVX, AVX2, AES, PCLMUL, FSGSBASE, RDRND, FMA, BMI, BMI2, F16C, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVEC, XSAVES, AVX512F, CLWB, AVX512VL, AVX512BW, AVX512DQ, AVX512CD, AVX512VNNI, AVX512BF16, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, ENQCMD, CLDEMOTE, PTWRITE, WAITPKG, SERIALIZE and TSXLDTRK instruction set support.

It's interesting it does not talk about AVX-512 for Alder Lake. So its very likely both Golden Cove and Gracemont supports AVX-2 but not AVX-512. AVX-512 continues to be an instruction for HPC.

Intel Tigerlake CPU with 64-bit extensions, MOVBE, MMX, SSE, SSE2, SSE3, SSSE3,

SSE4.1, SSE4.2, POPCNT, PKU, AVX, AVX2, AES, PCLMUL, FSGSBASE, RDRND, FMA, BMI,

BMI2, F16C, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVEC, XSAVES, AVX512F,

AVX512VL, AVX512BW, AVX512DQ, AVX512CD, AVX512VBMI, AVX512IFMA, SHA, CLWB, UMIP,

RDPID, GFNI, AVX512VBMI2, AVX512VPOPCNTDQ, AVX512BITALG, AVX512VNNI, VPCLMULQDQ,

VAES, PCONFIG, WBNOINVD, MOVDIRI, MOVDIR64B and AVX512VP2INTERSECT instruction

set support.

Gaming probably drove the core count decision. Well, that and the power draw.

It's weird Alderlake is an 8+8 configuration. That's actually the same amount of ring stops as 10 core Cometlake, possibly meaning they see ringbus as the limiter to scaling above that, and mesh doesn't work well for client.