-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

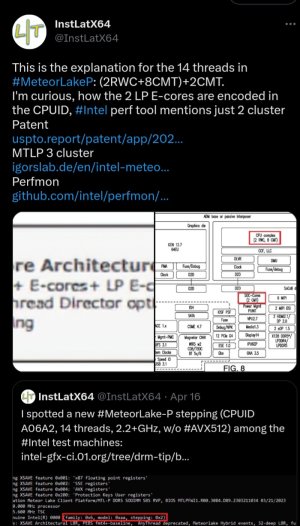

Discussion Intel current and future Lakes & Rapids thread

Page 798 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

Why do you think MTL may be cheaper to manufacture? Using tiles would minimize the increase but it is not going to make it cheaper. At least, not for a while if ever.Perhaps Intel 4/MTL is going better than we think and the Intel 7/Raptor Refresh is going to comprise 14 generation higher end while MTL, which may well be cheaper to manufacture will take the mid to lower shelf parts?

BorisTheBlade82

Senior member

Well, maybe not in the short term. But in the long term it is exactly the way to go. Just look at the ridiculous die sizes of EMR - and it will bring them nowhere near to competitiveness. Even an RTL successor would not be sustainable on newer nodes with all its badly scaling bloat on the same die.Why do you think MTL may be cheaper to manufacture? Using tiles would minimize the increase but it is not going to make it cheaper. At least, not for a while if ever.

Hopefully. But I think the economic part of Moore's law is dead. Performance and area scaling seems to be still happening. So unless you build a chip mixing and matching different process node, the cost savings won't be great even if you break up your giant chip into pieces.Well, maybe not in the short term. But in the long term it is exactly the way to go. Just look at the ridiculous die sizes of EMR - and it will bring them nowhere near to competitiveness. Even an RTL successor would not be sustainable on newer nodes with all its badly scaling bloat on the same die.

That's the reason why I don't think Intel will catch up to AMD in the server market until at least Granite Rapids comes out. I don't know if Granite Rapids will use multiple process nodes. But Sapphire Rapids and Emerald Rapids does not stand a chance.

On the desktop side, Intel's choice of using silicon interposer will limit how fast they can bring the cost down. It will be interesting to see what AMD does when they introduce real chiplet based APU. I'm sure they will delay using silicon interposer for as long as possible.

Hulk

Diamond Member

The reason for chiplets is economics so that is why I'm thinking that. Intel may be looking at transitioning from monolithic so chiplets sooner rather than later. Besides increasing yields by ditching the monolithic designs they can optimize process for various parts of the design.Why do you think MTL may be cheaper to manufacture? Using tiles would minimize the increase but it is not going to make it cheaper. At least, not for a while if ever.

BorisTheBlade82

Senior member

I think what the other user seems to be confused about is that it is cheaper..... for the manufacturer or in the case for amd for amd to pay for and tsmc doesn't waste much product that makes them look bad. Amd isn't going to give you a discount if it costs them less! they will keep the difference and charge you as much as they would have with a monolithic die.The reason for chiplets is economics so that is why I'm thinking that. Intel may be looking at transitioning from monolithic so chiplets sooner rather than later. Besides increasing yields by ditching the monolithic designs they can optimize process for various parts of the design.

intel going tiles with their own interconnect should be mighty interesting given the performance penalty it'll incur via latencies.

DrMrLordX

Lifer

That is a bit odd. It probably won't have much effect on adoption rate though.Hmm, that doesn't make much sense. Should be platform compatible.

I think it would. No idea if any of the cloud vendors will bother with EMR, but they absolutely hate having to certify new platforms. Wonder what the motherboard difference is, if anything.That is a bit odd. It probably won't have much effect on adoption rate though.

DrMrLordX

Lifer

Power delivery perhaps? Maybe there's a flaw in v1 of the platform? If Emerald Rapids is a substantially-better CPU then they'll do the validation one way or another. Sapphire Rapids can't be making vendors and system integrators very happy right now, except for those catering to the select audience that is better-served by Sapphire Rapids than competing products.I think it would. No idea if any of the cloud vendors will bother with EMR, but they absolutely hate having to certify new platforms. Wonder what the motherboard difference is, if anything.

nicalandia

Diamond Member

Curious, what are the performance limits of 2 E-cores?

Idle?

Updating apps in the background?

Web browsing?

Watching youtube?

Hulk

Diamond Member

I think web browsing and YouTube would be fine. Most videos are off-loaded to the GPU anyway.Curious, what are the performance limits of 2 E-cores?

Idle?

Updating apps in the background?

Web browsing?

Watching youtube?

My old Broadwell is stuck at .79GHz for some reason but I can still browse and watch Netflix and such on it.

BorisTheBlade82

Senior member

If I had to guess, I would say that web browsing will mostly take place on the compute tile for reasons of snappiness. Intel would not want to introduce stuttering - even if it was rather occasional.

The two SoC tile cores should really only be there for non time-critical background tasks like updates, cloud sync, AV, etc.

Also I would guess that these will be optimized for low voltage / low frequency.

The two SoC tile cores should really only be there for non time-critical background tasks like updates, cloud sync, AV, etc.

Also I would guess that these will be optimized for low voltage / low frequency.

Intel 14th Gen Core series to feature Meteor Lake-S is up to Core i5 and 65W TDP and Arrow Lake-S up to Core i9 125W - VideoCardz.com

Next-Gen desktop platform: Intel Meteor Lake-S up to 65W and Arrow Lake-S up to 125W Intel is now displaying products for the yet unannounced LGA-1851 desktop socket. It has been a while since there was any leak on the potential Meteor Lake-S desktop series, apart from rumors about its...

there are I9 SKUs with lower TDP like the 13900 and 13900TAlso ARL having lower TDP skus suggest MTL might end up being a stand alone generation rather than lumped in together with ARL, since ARL looks like it has its own low end skus.

Good catch. Totally forgot about those haha.there are I9 SKUs with lower TDP like the 13900 and 13900T

The slide saying "up to" i9 makes me think that the i9 won't be the only sku, and we will se a full lineup, but maybe it's just the i9s and i7s then?

Henry swagger

Senior member

Raptor refresh must be good if the is no i9 for meteor lakeHeavily suggests MTL will boost slightly upwards of 5 GHz if they are willing to release an i5 sku (the 13600k boosts up to 5.1 GHz) for ST.

Intel 14th Gen Core series to feature Meteor Lake-S is up to Core i5 and 65W TDP and Arrow Lake-S up to Core i9 125W - VideoCardz.com

Next-Gen desktop platform: Intel Meteor Lake-S up to 65W and Arrow Lake-S up to 125W Intel is now displaying products for the yet unannounced LGA-1851 desktop socket. It has been a while since there was any leak on the potential Meteor Lake-S desktop series, apart from rumors about its...videocardz.com

what the hell? isn't that the patents sheet link I posted 2 days ago?

not quite meteor is a clean up job like some short lived intel gens. I would get rpl refresh or wait it out until arrowlake.Raptor refresh must be good if the is no i9 for meteor lake

To me the real news of MTL will be that Intel 4 is up and running, yielding well and hitting decent clocks. Density and efficiency gains means Intel has a competitive process for the next architecture.

Can't really say that, assuming that Arrow's tile is being fabbed at TSMC. The 6+8 MTL CPU tile is not that big and the rest of the product is being fabbed elsewhere.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-