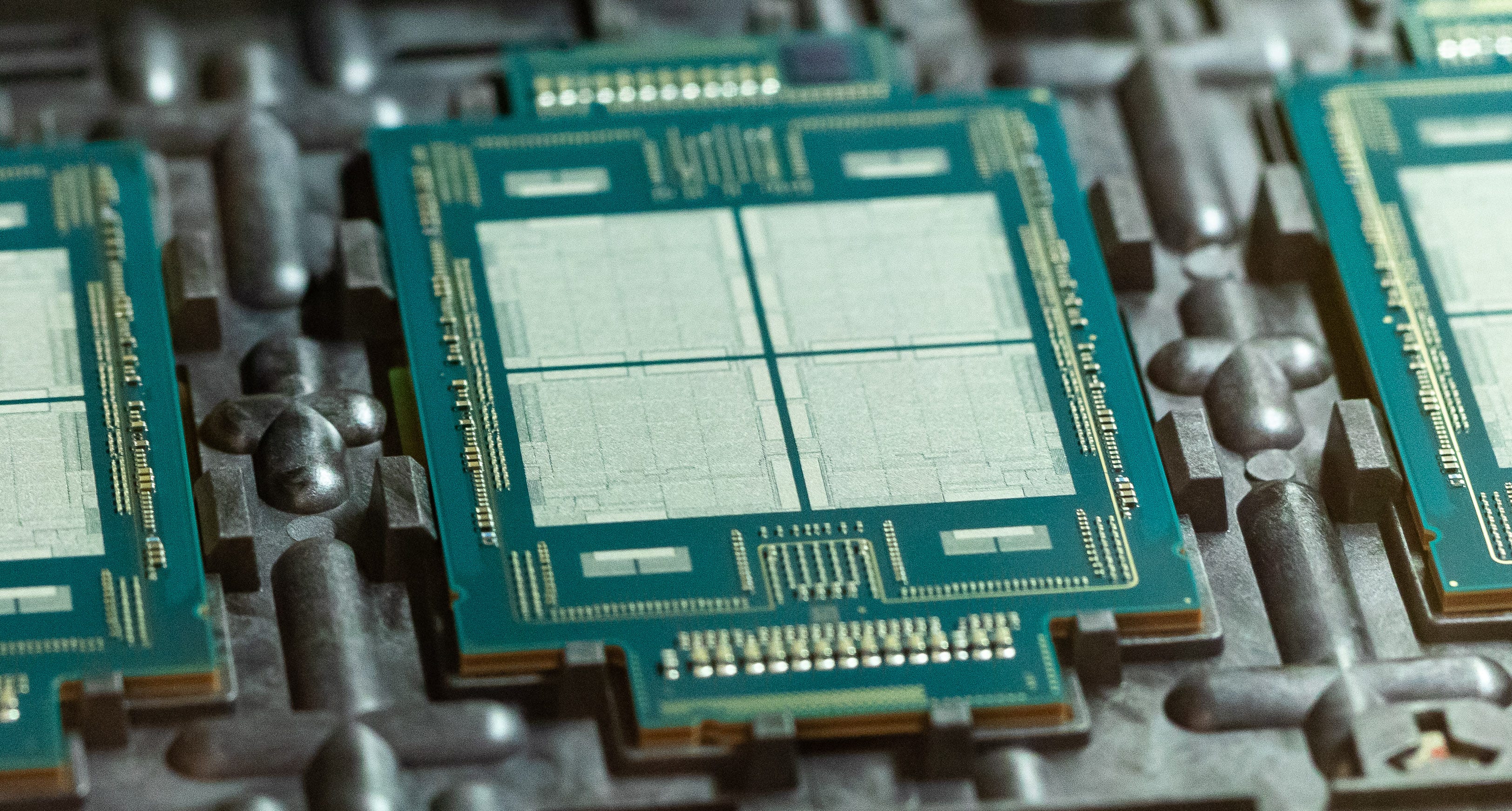

My measurements of the MTL client compute tile based on the wafer shots provided by Intel during the Intel Accelerated event are 4.85 mm x 8 mm = 38.8 mm², which checks out against Locuza's estimates. Pretty sure the larger center tile is actually the "SOC-LP" (despite being a total misnomer, that's the terminology Intel is using). It's huge because it's Intel 7 (née 10+++ / 10ESF) vs. Intel 4 (née 7nm), which is what the compute tile is made on. The skinny tile on the left is the GPU tile, which is comparatively tiny because it's TSMC N3. The little tile above the CPU die might be cache.

edit: The Foveros base die is probably the PCH, on either Intel 7 or good ol' 14nm. This would appear to be a single chip / mobile platform.

edit: The Foveros base die is probably the PCH, on either Intel 7 or good ol' 14nm. This would appear to be a single chip / mobile platform.

Last edited: