You can't have it both ways. It either doesn't change much or it does.

See Geekbench 5.2.5 for Zen 3 scores without new AES instructions. Here is a comparison between the same users 5600X

between v5.2.5 and v5.3.0

MT score doesn't really change (as it's cache/memory bound probably) ST AES improves roughly 35% (the overall ST score improves by ~30 points here)

It's a small bump to the overall score, but nothing major. In your own example, even if Crypto perf would be cut in half (which it won't), the Zen 3 would still score ~1635 points. I'd still call it a noticeable win.

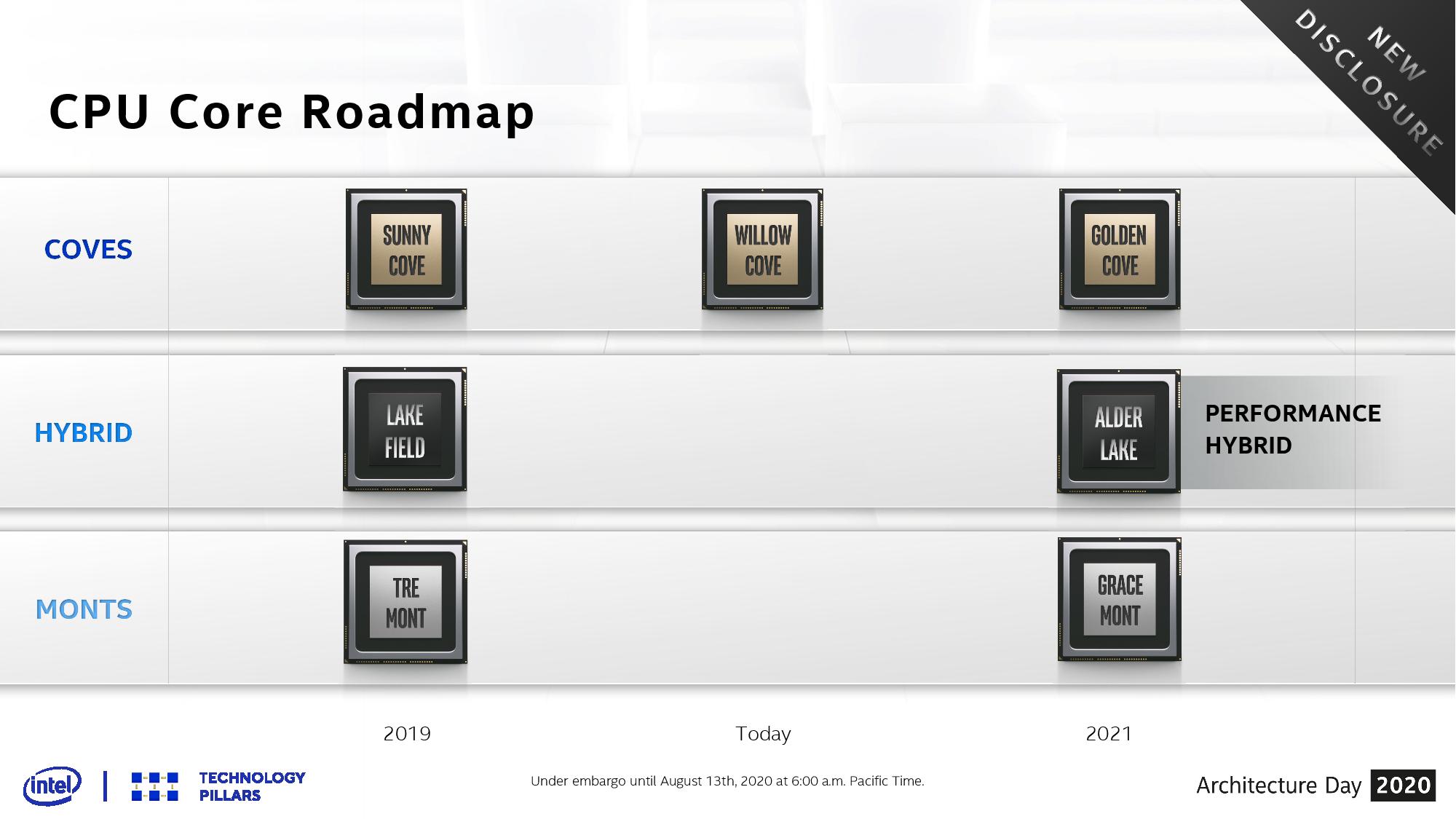

Regardless Judging from the i7 scores, it does appear that the main differentiator for Intel is the extra clocks and AVX-512 support. INT/FP IPC might be better but it's within margin of error. Still i9 will have even higher clocks, so there should be no doubt what will overall be faster.

I'd be really interested to see gaming results. I have no doubt Intel will win with extremely tuned memory and OC in all but most AMD cache-friendly titles (CS:GO, etc). At Stock and XMP would probably be more relevant to most users.