From what I see and hear from AMD I think Zen3 will exist on AM4 and AM5.

Due to their I/O die chiplets design they can just replace the I/O die for AM4 or AM5.

And since it's not on an 7nm+ process they can already test/build fine-tune DDR5 I/O now without delay.

That is one of the big advantages of using chiplets, early and smooth transition to DDR5.

You want to use your current DDR4 with the latest CPU design, no problem, not need to buy new DDR5.

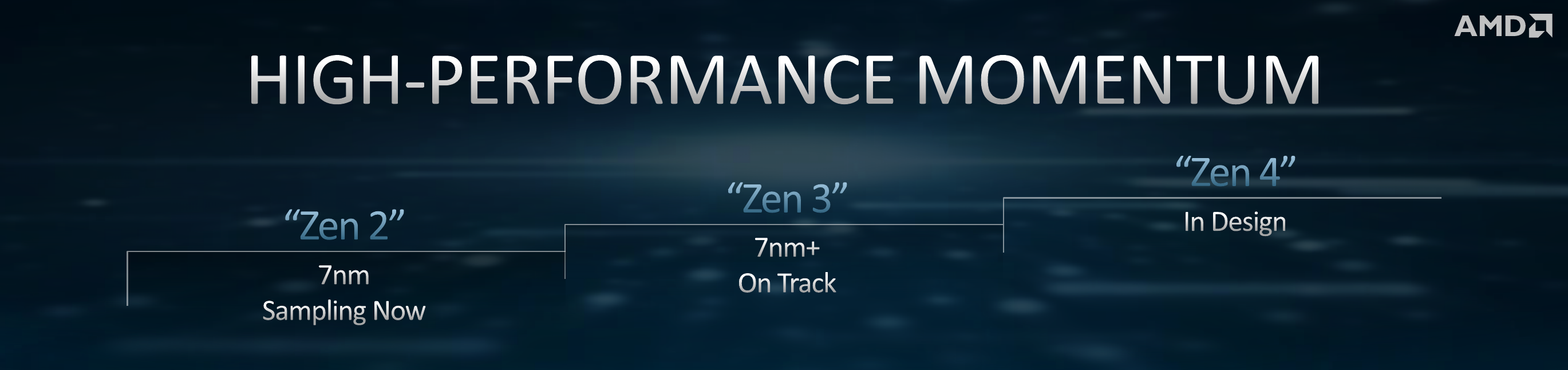

Also to avoid confusion, there is no Zen2+ it's called Zen3 although it's 7nm+