Die shots have always fascinated me, but I can never wrap my head around them. Features like the various caches are super easy to pick out, but I have no idea how people identify the other parts.

Some of it comes down to having looked at or studied a lot of other examples, because even though there's going to be changes and shifts in each processor, the overall architecture isn't going to undergo radical redesigns so you know what to expect. Any company that did do something completely new would be hyping it up so anyone paying attention would know to look for it. Otherwise the standard pipeline stages are pretty well defined and everyone knows what should be there.

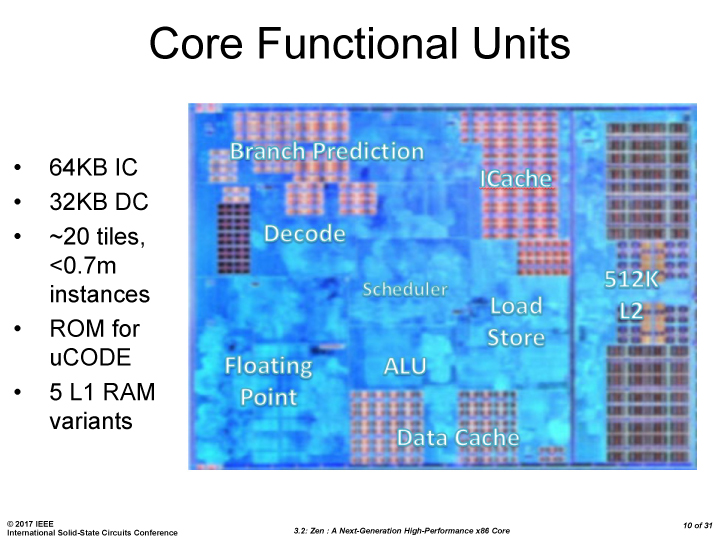

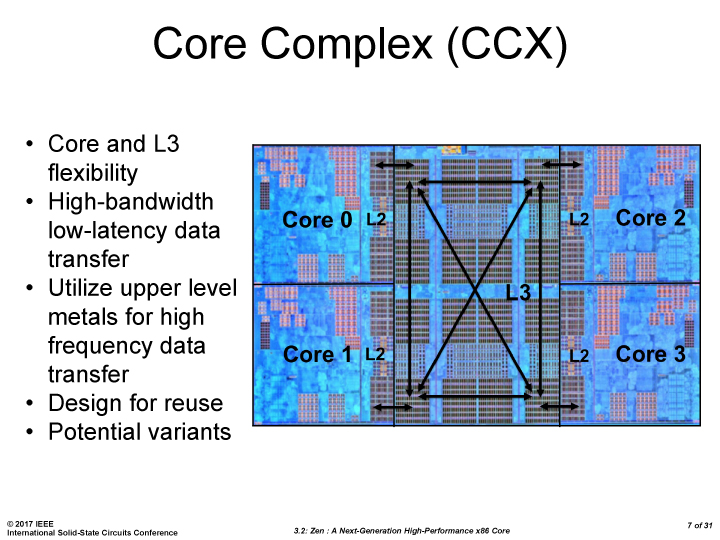

You can also block sections off based on where and how more prominent features are placed. The chip layout isn't going to have some winding border like a river or try to cram logic into every available crevice possible. Instead you'll get more clearly demarcated boundaries and some padding. Parts like the various caches especially tend to get laid out quite neatly which makes it easy to distinguish where the other parts are at.

Finally, some parts are just going to be physically located next to other parts because it makes it easier for them to communicate with other parts of the chip that they'll need to interact with most frequently. For example, you're going to want both the ALU and SIMD to have easy access to the data cache instead of having those all on opposite ends of the chip.