moinmoin

Diamond Member

Sashleycat combined the recently revealed Zen 2 core annotation with Fritzchens Fritz's hi-res die shots, and added the Zen 1 core as well for comparison:

Zen 2 core:

Zen 1 core:

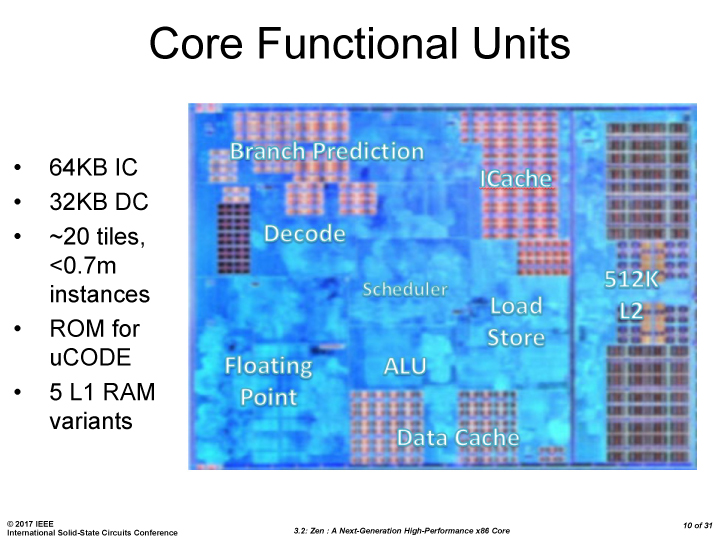

Zen 2 core:

Zen 1 core: