adroc_thurston

Diamond Member

- Jul 2, 2023

- 8,564

- 11,285

- 106

Well yeah it has twice the accessible L3.If my hunch is right Strix Halo should have higher single thread than Strix Point.

Well yeah it has twice the accessible L3.If my hunch is right Strix Halo should have higher single thread than Strix Point.

Or you can just quadruple the MALL with SoIC magicwaffen.

From 32 MB to 256 MB would be some jump, but if AMD were to use SoIC with two equally sized dies, there would be a lot of available die area.nope.

You can't hit this capacity in the bottom die.From 32 MB to 256 MB would be some jump,

You can't hit this capacity in the bottom die.

Bottom die needs a bajillion TSVs for power and ground to deliver the oomph for the compute on top.What is the bottleneck stopping it?

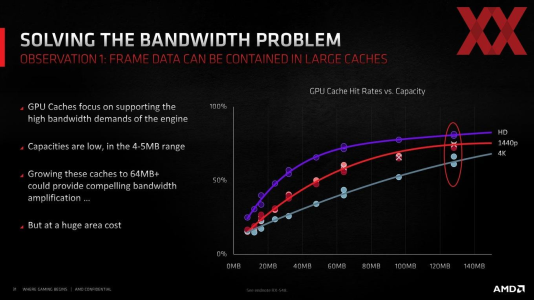

More than a bottleneck, it is probably a case of heavily diminishing returns for a noticeable increase in costs. I remember a graph about the hit rate of the cache against the size , which returned the bandwidth multiplier factor, and while the hit rate always increase with size, the increase went rapidly down after a certain amount of cache. 256 Mbytes was never used by AMD, even in the N21 case (128). N31 used 96 Mbytes for a 384 bit bus - and both these GPUs are classes above what Halo GPU is. 7800XT uses 64 Mbytes. I don't see Halo using more than 32 Mbytes for the reasons above.

RDNA3 went from 256 bit max to 384 bit max, memory clocks went up as well.I think after that graph AMD modified the caches in N3x and following, because with RDNA3 the cache size went down while they kept the efficiency at the same level. IIRC I did never see a similar graph for the RDNA3 architecture. Also, Strix Halo is not made for gaming at 4K for sure.

Not by much. Read bandwidth remains the same, only write bandwidth from IOD -> CCD has changed from 16B/clk to 32B.Also we can see how memory bandwidth affects rendering. If my hunch is right Strix Halo should have higher single thread than Strix Point.

I was more referring to the 7800XT, which is using 64Mbytes on a 256 bit bus even if the memories are faster in this case.RDNA3 went from 256 bit max to 384 bit max, memory clocks went up as well.

Well the SoC tile is N4P so you can probably figure out why it isn't there.@igor_kavinski Would like to see long idle tests to see if the rumored LPE cores are a thing (haven't seen any official material on it so it seems like it isn't true). The heavy load test is also very interesting as the M4 is supposed to have a significantly lower power limit and has a bigger battery, but is still showing less battery life. Probably the lowered scores for the AMD systems on battery is because they are reducing the power limit to have better battery life when under load whereas the Macbook doesn't lower the power limit (or not nearly as much) so performance doesn't drop significantly on battery, but then battery life takes a much bigger hit when under heavy load.

Well the SoC tile is N4P so you can probably figure out why it isn't there.

Plans changed or the N3E info was complete bogus.

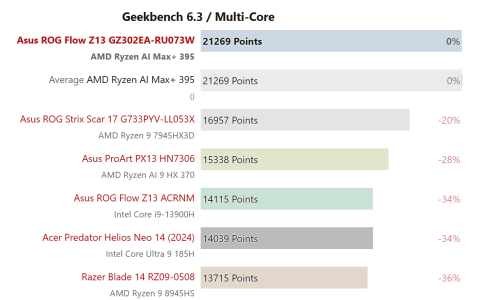

It does just fine vs M4 Pro when you consider the node disadvantage and the chassis being not ideal.

> The CPU can consume up to 86 Watts and then levels off at 70 Watts. the new Max+ 395 is comparable to the Ryzen 9 7945HX3D (Zen4) running at 115 Watts

> multi-core performance is very stable under sustained workloads