The only way to do that is moar SRAM, which directly translates to moar $$$ since SRAM scaling is Very Dead.

From a proc-centic POV thats correct, and I should have explained a bit more where I was aiming.

I think we are already well into the memory wall on the PC side now such that its going to become more and more an impediment even as we grind out smaller and smaller litho/uarch gains in the future.

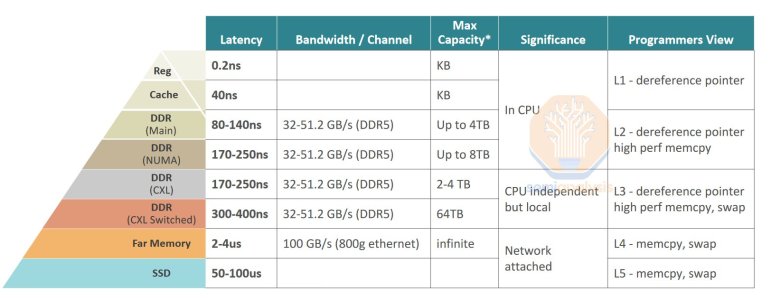

Everytime there is a cache miss the core has to go off-die to main memory, which causes n wait-states.

At 5ghz its n wait states

At 6ghz, its n + 20% wait states

Maybe it can do a context switch in the interim and do useful work, maybe not.

So our new 6ghz system is going to be faster than our old 5ghz potato, but we are not going to see significantly greater processing power as we might have in the past because cache-misses and off-die memory access is not improving at anywhere near the rate we've seen with proc architecture.

So even though our proc is 16% faster at 6ghz, every off-die memory access (non-cache) is burning more non-productive cycles in wait states at 6ghz vs 5ghz.

Now extrapolate from 5-6-7-8ghz, and there is only so much other work that can be done while waiting for memory return, and it would appear that the faster you go, the greater and greater off-die memory accesses are going to limit the actual work the proc can complete.

In fact its probably much worse because OS and people have doubled-tripled the number of processes and apps open at any one time such that I imagine a current cache-trace utility would show caches fragmented like crazy nowadays. Which then leads to more cache-misses and off-die requests slowing yet more.

So from a proc-centric POV, the faster we go without addressing memory speed, the lower and lower improvements we will be able to actually realize.

Semi-Analysis did an interesting video on the memory wall though he focused on economics and scaling vs efficiency and effects upon system throughput.

Making SRAM smaller/3d isn't going to really help, it'll be a crutch that will allow greater amounts of cache to hopefully prevent more cache-misses is all.

Knocking a zero off DDR latency would probably be like adding a Ghz or more to Core speed I would guess.