amd6502

Senior member

- Apr 21, 2017

- 971

- 361

- 136

I do not expect to see v1 big.Little or v2(DynamIQ) big.Little in any of the FDSOI nodes. Zen will stay on FinFETs/NextGen(Nanosheets), and designs that use CMT will stay on planar(FDSOI).

Zen races for desktop to HPC. High TDP/High Frequency/Big IPC focus

// Maintain TDP or increase TDP to get higher IPC to Frequency gains.

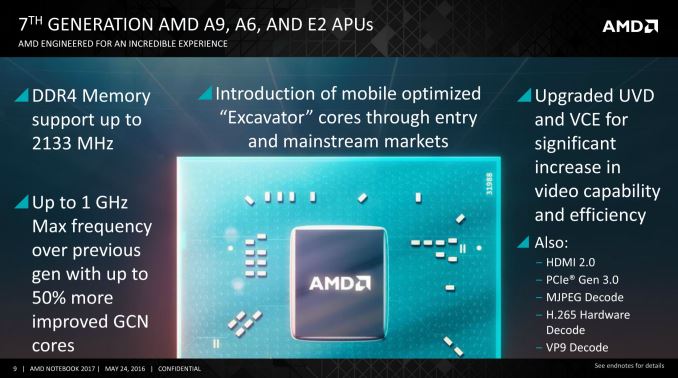

This core races for fanless to laptops. Low TDP/High Frequency/Big EPI focus

// Extends from Steamroller 35W -> Excavator 15W -> This core 7.5W

Wow, very informative. I kind of worry if they don't join the big.little crowd it could count against them for not having that feature. Also, amd pioneered the heterogenous computing idea and then seemed to have dropped it some years ago while arm plows ahead https://community.arm.com/processors/b/blog/posts/where-does-big-little-fit-in-the-world-of-dynamiq

I have little doubt that XV on an advanced 22FDX would be very perf/watt competitive at sub 10w---even without a next gen modification. I think they could easily do sub 10w for quadcore with L2 halved from BR's 2MB.

For the other performance end (DT+HPC) they could still mix planar with finfet cores for certain MCM products using their 8c/16t 7nm zen2 chiplet (if they ported a controller chip to planar). In fact, a small 22nm controller module and small iGPU for the consumer DT and mobile APU seems to make good sense, although with 16 threads I don't know if would make too much sense to mix in 4 XV or 8 puma cores (if they binned all the reject 4 core+below chiplets for consumer, then with 8 zen threads it almost would make sense to add those 4 to 8 little threads; but maybe not, and they just add an aSMT mode).