ZEN ES Benchmark from french hardware Magazine

Page 9 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

lolfail9001

Golden Member

- Sep 9, 2016

- 1,056

- 353

- 96

First ES? Doubt anyone has a clue.What was the clock of first 14nm INTEL batches?

First retail samples? Well, basically exact same as current Skylake sample clocks, just a pitch lower or higher.

Even then, though, those are different processes, anyways.

Do i really need to remind you they never demonstrated chip's power consumption, not to mention they have used a very light load for such illustration? Not to mention, what makes you think it was actually overvolted? Oh, and finally, name a single process that have improved in power consumption with a simple maturity nearly as severely as you suggest Zen shall. Intel failed to do so with actual node change, for pete's sake!AMD is going desktop first and demonstrated an overvolted 3.4GHz chip to draw less than 95W...

The "per core" part i don't remember. For all i care, they have compared a single core with 2 threads and a module power consumption wise. Here, a twist, and your forecast looks out of touch with reality.If we stick with AMD promise of same energy/clock per core as XV

I have no clue what FO4 either Zen or BW/SKL have. For all i care, it is irrelevant.Remember that Zen has lower FO4 than BW/SKL... Otherwise they couldn't manage to have higher clocks and lower power on an inferior process, with an overvolted ES...

Well the question is if this GF 14 HP will materialize at all. Looking at GF prior execution one can cast some doubt on it? Where is eg soi or some cheaper alternatives to finfet seronx was brabling about. Its gone i asume.

One can understand gf needs something higher perf than what goes into galaxy s9 but what is your take on what will happen?

We saw piledriver a year after bd with some easy gains. But zen looks far more balanced out the gate.

The quesion is. Will we see zen+ before 7nm? If yes. One should asume 14 HP is ready as amd hardly have ressources to just make a new zen+ on the same process they have now. Or what?

One can understand gf needs something higher perf than what goes into galaxy s9 but what is your take on what will happen?

We saw piledriver a year after bd with some easy gains. But zen looks far more balanced out the gate.

The quesion is. Will we see zen+ before 7nm? If yes. One should asume 14 HP is ready as amd hardly have ressources to just make a new zen+ on the same process they have now. Or what?

Whoops, sorry for not following that clearly. I don't know, I think they would have chosen 14nm HP from the beginning if that were the case. Zen doesn't look to be due for an update until Zen+ on 7nm in 2H '18.im not talking about Zen, originally we where talking about a Zen follow on and what process it would use. Which lead to the does GF actually run the 14nm process IBM created, to which i answered with it looks like it because the IBM chip architect calls the process GF 14nm HP.

Steamroller > Excavator (Carrizo) took almost a year and a half...instead of refreshing Zen on 14nm in 1H '18 I just see a 7nm release in Q4 '18 or Q1 '19 when 7nm @ GloFo is ready

...instead of refreshing Zen on 14nm in 1H '18 I just see a 7nm release in Q4 '18 or Q1 '19 when 7nm @ GloFo is ready

Yep i would asume that also.

But

A. Its 2 years out. Its a lot of time.

B. Secondly r&d budget have risen.

C. They dont have to pay debt now until like 2020. So there is cash.

D. The wsa point so them preparing for other possibilities.

All point to something happening before q1 2019.

itsmydamnation

Diamond Member

- Feb 6, 2011

- 3,138

- 4,007

- 136

They did bulldozer to piledriver in 12 months. I dont see why Zen would be any different. steamroller and excavator aren't good examples because they had other issues at the time like inventory management. There is like lots of low hanging fruit they can hit (much like piledriver) without making massive uarch changes.Whoops, sorry for not following that clearly. I don't know, I think they would have chosen 14nm HP from the beginning if that were the case. Zen doesn't look to be due for an update until Zen+ on 7nm in 2H '18.

Steamroller > Excavator (Carrizo) took almost a year and a half...instead of refreshing Zen on 14nm in 1H '18 I just see a 7nm release in Q4 '18 or Q1 '19 when 7nm @ GloFo is ready

Now the question we need to answer is that 12 months extra enough time to have based the design on 14nm HP.

Well the question is if this GF 14 HP will materialize at all. Looking at GF prior execution one can cast some doubt on it? Where is eg soi or some cheaper alternatives to finfet seronx was brabling about. Its gone i asume.

One can understand gf needs something higher perf than what goes into galaxy s9 but what is your take on what will happen?

We saw piledriver a year after bd with some easy gains. But zen looks far more balanced out the gate.

The quesion is. Will we see zen+ before 7nm? If yes. One should asume 14 HP is ready as amd hardly have ressources to just make a new zen+ on the same process they have now. Or what?

The Power9 design was done on IBM 14nm. That is completely different to GF 14nm ( Samsung 14nm ). Given the deal with IBM mandate the continue production my guess is that it will be on different team, and on low priorities.

The 22FDX , FD-SOI is actually right on track . Not sure if AMD will use it though.

Do i really need to remind you they never demonstrated chip's power consumption, not to mention they have used a very light load for such illustration? Not to mention, what makes you think it was actually overvolted? Oh, and finally, name a single process that have improved in power consumption with a simple maturity nearly as severely as you suggest Zen shall. Intel failed to do so with actual node change, for pete's sake!

Not at new horizont event, but at the twin event on december 8, for the press, under NDA, they showed the power consumtion and was about 94W difference between idle and full load (blender). Subtract PSU and VRM efficiency and you have under 80W. The video can be found in youtube and the link was given somewhere here on anand and all other forums... I don't know how come you have not seen it... Or maybe you are ignoring it...

The "per core" part i don't remember. For all i care, they have compared a single core with 2 threads and a module power consumption wise. Here, a twist, and your forecast looks out of touch with reality.

Here: http://www.anandtech.com/show/10591...t-2-extracting-instructionlevel-parallelism/8 5th slide. Take a look on the small foot note...

I have no clue what FO4 either Zen or BW/SKL have. For all i care, it is irrelevant.

How can zen draw less power than BWE at an higher clock with an inferior process? Magic? No! Lower FO4.

Hmm. I dont think its that simple and that there is conflicting information:They did bulldozer to piledriver in 12 months. I dont see why Zen would be any different. steamroller and excavator aren't good examples because they had other issues at the time like inventory management. There is like lots of low hanging fruit they can hit (much like piledriver) without making massive uarch changes.

Now the question we need to answer is that 12 months extra enough time to have based the design on 14nm HP.

Where should the low hanging fruit be looking at the zen results?

For bd they eg implemented a clock mesh technology. And could improve freq to where it was intended.

And loking at how late gf 14nm was implemented i seriously have doubt they could ready in a year. As say work on improving yield on existing process.

What i think looking at the results is that amd should have plenty access to funding for new activities be it arch or process work. Unlike the last 10 years they are in a good position. With a ceo really fit for where the company is going and a good roadmap.

The Power9 design was done on IBM 14nm. That is completely different to GF 14nm ( Samsung 14nm ). Given the deal with IBM mandate the continue production my guess is that it will be on different team, and on low priorities.

The 22FDX , FD-SOI is actually right on track . Not sure if AMD will use it though.

It looks like a bit of mess to me. A lot of nodes and few ressources. It doesnt add up.

1. Power 9 14nm hp process

2. 22FDX

3. FD-soi

4. 14 lpp

5. 7nm

Yep they skipped 10nm. No sh!t. That was a tough choice. Lol.

And who is the buyer besides amd? How many power9 is sold.

But yeaa if ibm can fund the 14HP nearly 100% there is a bit of sense but...

itsmydamnation

Diamond Member

- Feb 6, 2011

- 3,138

- 4,007

- 136

Hmm. I dont think its that simple and that there is conflicting information:

Where should the low hanging fruit be looking at the zen results?

For bd they eg implemented a clock mesh technology. And could improve freq to where it was intended.

And loking at how late gf 14nm was implemented i seriously have doubt they could ready in a year. As say work on improving yield on existing process.

What i think looking at the results is that amd should have plenty access to funding for new activities be it arch or process work. Unlike the last 10 years they are in a good position. With a ceo really fit for where the company is going and a good roadmap.

Exactly the same kind of stuff the did with PD, improve prefetch and predict improve handling of edge case ops, further tuning of SMT weights/priorities, increases to queue sizes, further improvement in memory disambiguation etc etc. All of these features you don't just do once you continually iterate on them. But Zen is the first in the line and you are never going to get everything perfect first time around.

If they move to HP there is likely to be more clocking head room, Power9 is shipping H2 17 so Q1 18 14HP should be well on its way. So you could end up with that 5-10 points of IPC (depending on workload) and a few hunder extra Mhz on base and or turbo.

It looks like a bit of mess to me. A lot of nodes and few ressources. It doesnt add up.

1. Power 9 14nm hp process

2. 22FDX

3. FD-soi

4. 14 lpp

5. 7nm

Yep they skipped 10nm. No sh!t. That was a tough choice. Lol.

And who is the buyer besides amd? How many power9 is sold.

But yeaa if ibm can fund the 14HP nearly 100% there is a bit of sense but...

22FDX = FD-SOI. So you could count one out. 7nm is future tense, so doesn't count either.

While no products are out yet, 22FDX

theoretically offer slightly better characteristics at low power and slightly cheaper then 14/16nm FinFET. It is suppose to be a good fit for IoT or any other price sensitive controller still on 28nm.( I am thinking of Qualcomm with the NXP acquisition )

Last edited:

lolfail9001

Golden Member

- Sep 9, 2016

- 1,056

- 353

- 96

1. You do not account for PSU efficiency not being a constant.Not at new horizont event, but at the twin event on december 8, for the press, under NDA, they showed the power consumtion and was about 94W difference between idle and full load (blender). Subtract PSU and VRM efficiency and you have under 80W. The video can be found in youtube and the link was given somewhere here on anand and all other forums... I don't know how come you have not seen it... Or maybe you are ignoring it...

2. My point about load being light stands, though i do expect that in Prime95, Zeppelin will consume significantly less than BWE.

Footnote relates to the asterisk on "work per cycle". Energy per cycle does not have a single foot note relating to what it compares. So, my theory about it being module vs SMT core stands. What now? Oh, and btw, you may just right, and it does compare core for core. But then don't you find it funny for your claim that power consumption per cycle did not drop one iota despite such a ridiculous node shrink?Here: http://www.anandtech.com/show/10591...t-2-extracting-instructionlevel-parallelism/8 5th slide. Take a look on the small foot note...It says explicitly 1 core vs 1 core, zen vs excavator... Since 1 isolated XV core does not exist, this means 2 zen core draw same power of an XV module. It's all simple like that. But somehow you ignored it...

1. BWE was running at higher clock, actually.How can zen draw less power than BWE at an higher clock with an inferior process? Magic? No! Lower FO4.

2. BWE has a proper separate chipset and way larger uncore with it, Zeppelin from all we know... not quite.

See, and i did not even need to bring up EE for nothing.

1. You do not account for PSU efficiency not being a constant.

2. My point about load being light stands, though i do expect that in Prime95, Zeppelin will consume significantly less than BWE.

Constant or variable, they are max 90% both. 80W is an upper limit. This is an ES and as I said, in other forums was said that was overvolted, so let's wait for retail with turbo and XFR enabled.

Footnote relates to the asterisk on "work per cycle". Energy per cycle does not have a single foot note relating to what it compares. So, my theory about it being module vs SMT core stands. What now? Oh, and btw, you may just right, and it does compare core for core. But then don't you find it funny for your claim that power consumption per cycle did not drop one iota despite such a ridiculous node shrink?

A zen core actually should have moreless the same transistors as an XV module. It has half the decoders, half AGU and L/S units, less L2, one L1D albeit bigger, a smaller L1I and its FPU can't do FMACs natively. Moreover the uop cache and other enhancements are said to reduce power. Even if zen was on the same 28nm BULK it probabily would consume same as a whole XV module, let alone on a 2 node better process!

1. BWE was running at higher clock, actually.

2. BWE has a proper separate chipset and way larger uncore with it, Zeppelin from all we know... not quite.

See, and i did not even need to bring up EE for nothing.

Let's decide. When comparing performance "but 6900K has 3.2GHz base clock! So it's faster clock to clock!!!", when comparing power "but 6900k has turbo and go at 3.5GHz!!!". Either has higher IPC than Zen or draw less power at same clock. Not both...

EDIT. Moreover Zen is a SoC, BWE, not. It has PCIex, MC, USB, Sata, GB ethernet... I am not sure that BWE has on die USB, sata and GB ethernet...

Last edited:

Well if 14HP is running as you outline surely it makes sense for a q1 18 slightly facelifted zen. I wouldnt bet on excess of 5%.Exactly the same kind of stuff the did with PD, improve prefetch and predict improve handling of edge case ops, further tuning of SMT weights/priorities, increases to queue sizes, further improvement in memory disambiguation etc etc. All of these features you don't just do once you continually iterate on them. But Zen is the first in the line and you are never going to get everything perfect first time around.

If they move to HP there is likely to be more clocking head room, Power9 is shipping H2 17 so Q1 18 14HP should be well on its way. So you could end up with that 5-10 points of IPC (depending on workload) and a few hunder extra Mhz on base and or turbo.

Surely such a solution solves the waiting for q1 19 7nm.

Lets hope for that.

lolfail9001

Golden Member

- Sep 9, 2016

- 1,056

- 353

- 96

You do not account for PSU efficiency improving with load on most of decent PSUs. Using the OP article, we learn that with VRMs 3.3Ghz Zeppelin consumes about 94W on light load. Even assuming it is one of the earlier samples that it is not, there is a long road to your claim on clocks to power consumption.Constant or variable, they are max 90% both. 80W is an upper limit.

Sure, quote me on the sentence you attribute to me.Let's decide.

Since they were measuring system performance, it actually plays in favor of BWE power consumption wise. I'll let you figure out how. But anyways, there is little to discuss now, because while it is entirely possible Zeppelin will get a 20% clock uplift over what was shown in Canard article, it most certainly won't happen in the same power envelope.I am not sure that BWE has on die USB, sata and GB ethernet...

Zstream

Diamond Member

- Oct 24, 2005

- 3,395

- 277

- 136

EDIT. Moreover Zen is a SoC, BWE, not. It has PCIex, MC, USB, Sata, GB ethernet... I am not sure that BWE has on die USB, sata and GB ethernet...

What do you mean? Why would AMD add that to their processor, increasing thermal power and increase die size?

It is most likely the higher end AM4 motherboards do have additional chips onboard to provide more PCI-E lanes,etc.

It drops power consumption for the platform,and means they can use cheaper motherboards.

Look at what Intel has done with the Xeon D.

What do you mean? Why would AMD add that to their processor, increasing thermal power and increase die size?

It drops power consumption for the platform,and means they can use cheaper motherboards.

Look at what Intel has done with the Xeon D.

What do you mean? Why would AMD add that to their processor, increasing thermal power and increase die size?

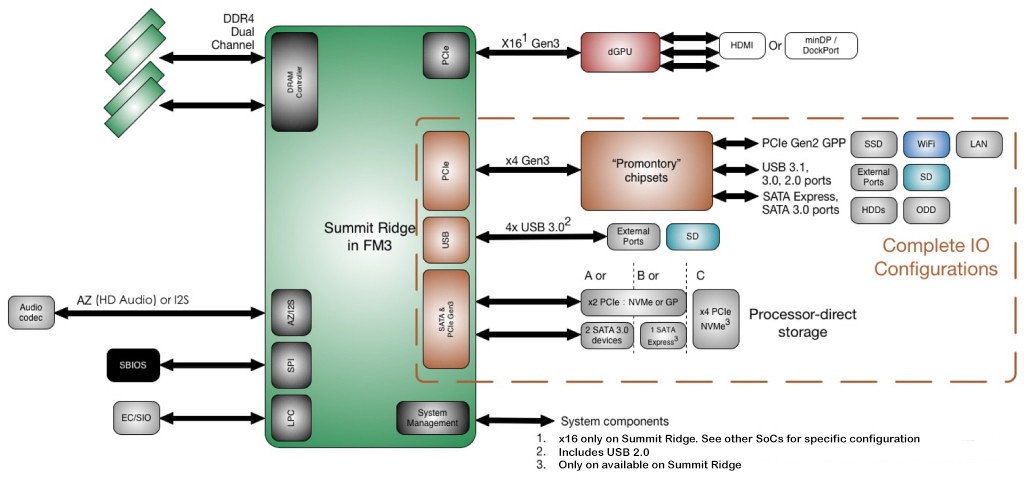

http://www.kitguru.net/components/c...r-direct-nvme-storage-promontory-pch-usb-3-1/

You do not account for PSU efficiency improving with load on most of decent PSUs. Using the OP article, we learn that with VRMs 3.3Ghz Zeppelin consumes about 94W on light load. Even assuming it is one of the earlier samples that it is not, there is a long road to your claim on clocks to power consumption.

I was talking of new horizon test, the event of december 8, where load-idle is about 93-94W. Here the consumption is at the wall. We have here a chip nearer to retail than the ES of Canard PC. Anyway the VRMs efficiency is max 90% in ideal conditions and the PSU only if is "gold" has 90% max efficiency. If it's bronze can have even 80%.

In synthesis:

- New Horizon event: newer chip, 94W delta at the wall, subtract 10+10% for efficency and you have under 80W.

- Canard PC: older ES (3.15GHz), 94W delta on the 12V rail. Subtract 10% for VRM and you have 85W.

And these are upper limit, because the efficiency are the theoretical limit. Measured efficiency for quality VRMs are in the range of under 88%. I rounded a bit in excess...

Sure, quote me on the sentence you attribute to me.

Since they were measuring system performance, it actually plays in favor of BWE power consumption wise. I'll let you figure out how. But anyways, there is little to discuss now, because while it is entirely possible Zeppelin will get a 20% clock uplift over what was shown in Canard article, it most certainly won't happen in the same power envelope.

In the new horizon event the consumption includes the chipset in both cases, with BWE that have more in the SB and less in the CPU.

In the CanardPC review I assume that the 12V rail is the one that power the CPU only, so in the case of BWE the USB, sata and gigabit ethernet are not accounted in the consumption, favouring Broadwell...

As explained AM4 CPUs are true SoCs. On inexpensive motherborads or small form factor or in notebook/tablets, all that integrated in the CPU is sufficient, so no external chips are needed. Only premium motherboards need external chipset.What do you mean? Why would AMD add that to their processor, increasing thermal power and increase die size?

AFAIK the AMD SoCs have also integrated NVMe, Audio and USB 3.1... So you don't need much stuff out of the CPU...

SlowSpyder

Lifer

- Jan 12, 2005

- 17,305

- 1,002

- 126

When was the last time Intel had to lower prices in the enthusiast / desktop space due to competition? I really hope these early benches have merit. This is an encouraging sign whether you want to buy AMD or Intel for your next build.

I'd love to see a 2C/4T or 3C/6T Zen core APU with good clocks, give it 12-14CU's/768-896SP's (Polaris) and some fast DDR4.

I'd love to see a 2C/4T or 3C/6T Zen core APU with good clocks, give it 12-14CU's/768-896SP's (Polaris) and some fast DDR4.

Arachnotronic

Lifer

- Mar 10, 2006

- 11,715

- 2,012

- 126

When was the last time Intel had to lower prices in the enthusiast / desktop space due to competition? I really hope these early benches have merit. This is an encouraging sign whether you want to buy AMD or Intel for your next build.

Phenom II?

When was the last time Intel had to lower prices in the enthusiast / desktop space due to competition? I really hope these early benches have merit. This is an encouraging sign whether you want to buy AMD or Intel for your next build.

I'd love to see a 2C/4T or 3C/6T Zen core APU with good clocks, give it 12-14CU's/768-896SP's (Polaris) and some fast DDR4.

As a ccx is 4 cores my bet is smallest APU is just that. I guess BR will take lowest end until 7nm comes q1 2019.

As for the gpu part surely its ddr4 at first but its going to be vega arch i think using the same fantastico fabric

Yep. It seems so.Phenom II?

Fortunately the compettition had a slight effect right up to sb and also sb in laptops.

Penryn was a fantastic cpu especially for mobile. Good freq headroom and a huge cache for the top models. Westmere was hardly a step forward here on laptops. On desktop 920 was a blast and amd was way beyond.

Now having bought a pc in 1990 where both 286 386 and 486 was sold to consumers its safe to say that if amd had not been here even with a crappy bd arch Intel segmentation would have been far more agressive. Think sb beeing sold along side skl. And btw the performance difference here is less than between 386 and 486.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 23K

-

-

AnandTech is part of Future plc, an international media group and leading digital publisher. Visit our corporate site.

© Future Publishing Limited Quay House, The Ambury, Bath BA1 1UA. All rights reserved. England and Wales company registration number 2008885.