igor_kavinski

Lifer

Pretty sure that would be a severe violation of the Geneva Convention 😀That's too easy they get to use i486 and use windows dos

Pretty sure that would be a severe violation of the Geneva Convention 😀That's too easy they get to use i486 and use windows dos

tbf it's not like there wasn't insane global trade conditions created by the supply chain knock on effects of COVID and associated inflation.Hasn't each follow on generation taken longer?

...Verano is _NOT_ the successor to Venice, it is a Venice variant.

Florence is Venice+1 ...

The question is does +1 mean +1 generation as in Zen7, or does it mean something else?Florence anybody ??

Florence means AMD will stop naming their EPYCs after Italian cities and start using names from The Jeffersons and 227.The question is does +1 mean +1 generation as in Zen7, or does it mean something else?

APX is excellent but unlikely to be introduced untill Zen 7APX - I think excellent. With Intel adding it likely in Diamond Rapids in 2026, there should be some software and compiler support. And it seems like this would be only a modest change to the CPU, centered on the decoder. So seems like a very easy addition leading to some cleanup of the x86 code. But it will likely take years for the software support to find its way to client applications.

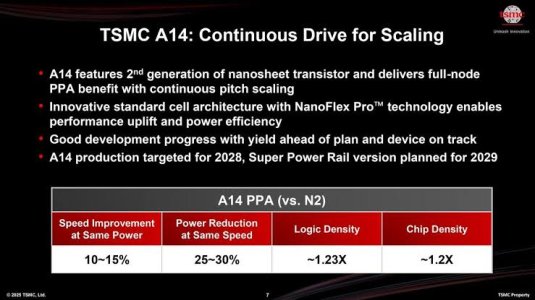

The logic xtor gain from N2 to A14 is mere 1.23X. AMX is fine for server thoughAMX - AMD will find itself with a huge transistor budget increase from Zen 6 to Zen 7, if L3 completely moves to V-Cache level. If ~33% of die area migrates to V-Cache, that leaves +50% increase in die size availability, and then, going from N2 -> A16 -> A14 could add another ~50% logic transistor density increase. So, possibly, doubling transistor budget.

APX is excellent but unlikely to be introduced untill Zen 7

The logic xtor gain from N2 to A14 is mere 1.23X. AMX is fine for server though

View attachment 127761

Well... for AMD I agree. Intel seems to believe the die space is better utilized for E cores.... at least for the time being.SMT is forever.

What the I legit thought it was a Zen 6 thread 🤣🤣

Well... for AMD I agree. Intel seems to believe the die space is better utilized for E cores.... at least for the time being.

The idea that Zen 7 will be released within a year of Zen 6 would require that the reality of the world of lithography be drastically reversed.

AMD has been taking between 18-24 months between generational releases. I personally don't expect this to get LOWER. If anything it will get HIGHER.

In DC, it seems more likely they will push forward with A14. I personally don't see why AMD wouldn't greatly increase core counts with Zen 7c in DC.

Doubtful. It's not new, so the Cadence should have been shortened before now. But it didn't. The designs simply grew instead.So it is possible that AI tools will shorten the cadence

Core logic includes structures that are characterized by some latency due to their single-plane nature. For example, the edges of these planes/regions of a given logic. A single logic plane can be problematic when expanding across generations. Splitting a given piece of logic into two layers reduces the logic's latency and shortens critical paths.Not sure I buy into the concept that they somehow need a multi layer core to get more IPC, unless it's just about reducing IO wire lengths between certain parts of the core.

Regarding Zen5, people have blown their own bubble based on the Epyc (Zen5) results.ngl with the less than mind blowing perf uplift of Zen5 after years of hype I'm starting to feel that someone is trying to generate that kind of pre release hype train here.

Interesting, I thought it would be higher. Then, the A16 and A14 seem like half nodes...

Where have you been? Every node is a half node now...quarter node really.

Well yeah metal scaling is ass.23% increase in logic density from 2 nodes seems on the low end even for 2 half nodes.

I feel like extrapolating from CCD transistor count is not a solid enough lead to use, if that is what you are using to get to this figure.Zen5 has about 26% more transistors per core, or about 218 million

Until official data for the Zen5+L2 core is available, this is the only way.I feel like extrapolating from CCD transistor count is not a solid enough lead to use, if that is what you are using to get to this figure.

That's basically what I meant by the comment you responded to.Core logic includes structures that are characterized by some latency due to their single-plane nature. For example, the edges of these planes/regions of a given logic. A single logic plane can be problematic when expanding across generations. Splitting a given piece of logic into two layers reduces the logic's latency and shortens critical paths.

Well, why wouldn't AMD use the Verano name for new EPYC series or why would that be a mistake?AMD marketing team is amateurish, the name of the italian city is Verona, look like

Lisa Su is unaware of this city since she publicly made the typo.