There is no bitcell shrink it's a SRAM Macro Shrink.Well, for what it's worth, L3/SRAM scaling on all of TSMC's non-specialized libraries from N5 all the way to N3E have had a big fat zero in SRAM scaling improvement.

N2 is the first node after a long time that improves on it. A relatively generous ~17% shrink.

I'm betting this was one of the big factors in AMD wanting to splurge all-in for N2 across the board with Zen6 designs.

You can have your extra cores shrink all you want for your CCDs, they're tiny anyway, but if that 24/48MB/64MB/whatever L3 needs 50% more die space, that ain't good.

-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Zen 6 Speculation Thread

Page 244 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

LightningZ71

Platinum Member

It's PRIMARILY a macro shrink, but, there is a little bit-cell shrinkage in N2. BSPDN should manage to shrink the macro a bit once it's implemented due to relocating the power wires. I think Tom's had an article that gave a bit more detail. If memory serves, the shrinkage is not advertised as a benefit due to how small it is, and is largely math extrapolated from other published numbers.

Until they go 3D with the cells, find a way to make 4T work well enough in current applications, or reimagine the whole cell to take better advantage of lithography changes over the last decade, it's not shrinking much more.

Until they go 3D with the cells, find a way to make 4T work well enough in current applications, or reimagine the whole cell to take better advantage of lithography changes over the last decade, it's not shrinking much more.

there is none according to TSMCbut, there is a little bit-cell shrinkage in N2

Thunder 57

Diamond Member

there is none according to TSMC

From the same source as Adroc?

adroc_thurston

Diamond Member

Nnnnope.there is a little bit-cell shrinkage in N2

They did publish N2 stuff at like ISSCC iirc.From the same source as Adroc?

From the same source as Adroc?

adroc_thurston

Diamond Member

see my memory wasn't wrong, it was ISSCC.

lol i knew thatsee my memory wasn't wrong, it was ISSCC.

Yea, the leak they are talking about showed some IOD configurations and people extrapolated to the core counts. I don't believe that AMD has stated what core counts will be supported for full Zen 6.For the record let me just say that I never said anything about Zen 6 classic being limited any specific number of core counts until I was told by someone else that I did. After which I only questioned why it would drop from current Zen 5 counts.

Apparently I missed this roadmap leak everyone is talking about. The most recent one I can find is the one for mobile mentioning "Gator Rande".

View attachment 130437

I still am not seeing the logic behind going from 128 full Zen 5 cores to 96 Zen 6 cores. For workloads that need the higher performance cores, there is no way this ISN'T a step backwards ..... which again simply doesn't make any sense.96 Zen 6 Core would likely be limited to SP8 and 8 Ch memmory and 256C would require SP7 you can easily pack 8 Zen6 CCX and it doesn't require 16 Ch memory.

I will be delighted to look back on this thread and either state "See, it didn't make any sense", or "Wow. You were right"; however, at this time, I am in the "It doesn't make any sense" camp.

adroc_thurston

Diamond Member

Because you're going from 64c Z5c of Sorano to 96c Z6 for Venice SP8.I still am not seeing the logic behind going from 128 full Zen 5 cores to 96 Zen 6 cores

SP5 Turin Classic has no successor.

Markfw

Moderator Emeritus, Elite Member

My 9755 is absolutely kicking ass in the current DC competition that is very avx-512 dependant. And at 100% load its doing 64 c CPU temp WITH AN AIR COOLER !Because you're going from 64c Z5c of Sorano to 96c Z6 for Venice SP8.

SP5 Turin Classic has no successor.

You can't say enough good things about Turin,.

LightningZ71

Platinum Member

I think that people are failing to see the big change for this generation and not seeing where it will make the most difference. The "c" core CCD is rumored to have the same total amount of L3 cache as the normal core CCD. It's still less per core, but the total local pool is much larger. In addition, with the node improvement, even if just from N3, you still get a notable improvement in throughput per watt. I suspect that, in many cases, 128 cores of Zen 6c will be faster than regular Zen5, and I don't think that there will be a notable difference in all core steady state clocks under load with Zen6 possibly doing better.

CouncilorIrissa

Senior member

That's already the case with Turin-D, the dense CCD has 32MB of L3.I think that people are failing to see the big change for this generation and not seeing where it will make the most difference. The "c" core CCD is rumored to have the same total amount of L3 cache as the normal core CCD. It's still less per core, but the total local pool is much larger. In addition, with the node improvement, even if just from N3, you still get a notable improvement in throughput per watt. I suspect that, in many cases, 128 cores of Zen 6c will be faster than regular Zen5, and I don't think that there will be a notable difference in all core steady state clocks under load with Zen6 possibly doing better.

adroc_thurston

Diamond Member

No?The "c" core CCD is rumored to have the same total amount of L3 cache as the normal core CCD

Dense is 128M, classic is 48M L3$.

they're all N2p.In addition, with the node improvement, even if just from N3, you still get a notable improvement in throughput per watt

adroc_thurston

Diamond Member

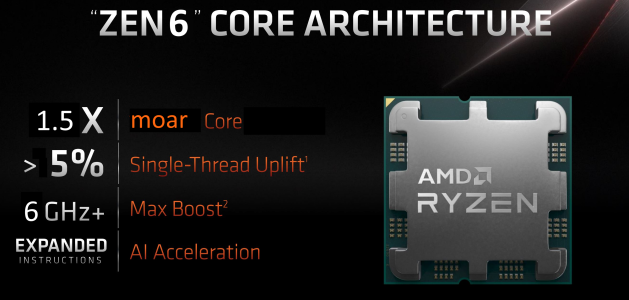

boring, fix your numbersView attachment 130533

OFFICIAL FAN SLIDEWARE for ZEN 6 (Desktop)

Comments, concerns?

I believe we have this nailed.

gdansk

Diamond Member

After painstakingly reviewing paint I remain confident these are the best numbers. I am not a fan of 42% personally.boring, fix your numbers

adroc_thurston

Diamond Member

you're getting 70% moar for Venice doe.I am not a fan of 42% personally.

so fix your numbers.

blackangus

Senior member

You forgot:OFFICIAL FAN SLIDEWARE for ZEN 6 (Desktop)

Comments, concerns?

I believe we have this nailed.

1: Or less

2: In the arctic circle

adroc_thurston

Diamond Member

and need a bulletpoint for gen3 Vcache.You forgot:

1: Or less

2: Maybe

Ain't no way AMD's not gonna dangle the crackpipe in front of thirsty-thirsty gamers.

LightningZ71

Platinum Member

That's considerably more than I expected. So, that's the same L3 per core...No?

Dense is 128M, classic is 48M L3$.

I meant going from Zen5p ccd to Zen6c CCD, that's going from N4x/p to N2. That's quite a jump...they're all N2p.

adroc_thurston

Diamond Member

Yeah, favelas wanted that.So, that's the same L3 per core...

You're jumping to N2p for everything but mainstream mobile parts.I meant going from Zen5p ccd to Zen6c CCD, that's going from N4x/p to N2. That's quite a jump...

V cache at this point interests me for one reason, and one reason only.and need a bulletpoint for gen3 Vcache.

Ain't no way AMD's not gonna dangle the crackpipe in front of thirsty-thirsty gamers.

That being the possibility of a future generation completely eliminating L3 (and possibly even L2) cache off the main logic die.

Honestly when MLID started blarting about a 3D core for Zen7, this is what I was assuming he was talking about.

adroc_thurston

Diamond Member

yeah.That being the possibility of a future generation completely eliminating L3 (and possibly even L2) cache off the main logic die.

oh nooo 3D core is something wayyyyy different. Forget about it for a moment.Honestly when MLID started blarting about a 3D core for Zen7, this is what I was assuming he was talking about.

gdansk

Diamond Member

Intel has been trying to make this work for a certain forest for years now. Lots of slideware available on that.That being the possibility of a future generation completely eliminating L3 (and possibly even L2) cache off the main logic die.

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 24K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-