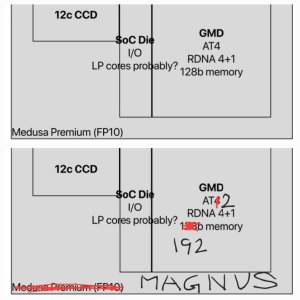

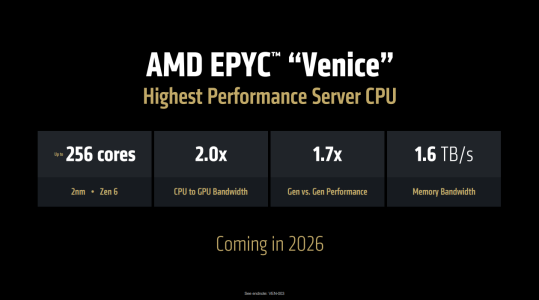

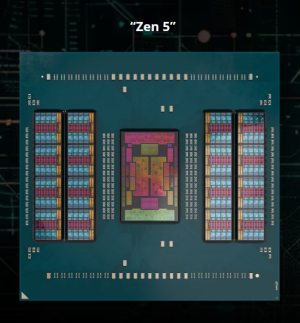

If AMD and intel start to intruduce ''big APUs'' to the PC market. isn't it possible that they decide that low-mid MOBOs don't need a PCIe slot for an external GPU because they wouldn't be adding that many pcie lanes to their APUs... threatening NVIDIA gaming GPUs?

Why would you want to buy a X050-X070 NVIDIA GPU if to do that you need to buy a very very expensive high end mobo and a very expensive hig end CPU with enough pcie lanes, but you can buy a cheap MOBO + a not-so-cheap big APU if you want a gaming PC? or a cheap mobo and a cheaper cpu with an smaller iGPU for office.

Why would you want to buy a X050-X070 NVIDIA GPU if to do that you need to buy a very very expensive high end mobo and a very expensive hig end CPU with enough pcie lanes, but you can buy a cheap MOBO + a not-so-cheap big APU if you want a gaming PC? or a cheap mobo and a cheaper cpu with an smaller iGPU for office.