More Zen 6 speculation, because this is a speculation thread and we need more pages. Read on, the shat could get a bit deep. On potential MT uplift:

Zen 1 to Zen 2 was Samsung/GF 14nm to TSMC 7nm. R7 1800X and R7 3800X were 95/105W TDP SKUs, all same number of cores (8). Using Cinebench R15 MT, we get:

R7 1800X: 1617 CB

R7 3800X: 2164 CB

-------------------------------

+34%

Zen 3 to Zen 4 was TSMC 7nm to TSMC 5nm. R7 5900X & R7 7900X were both 105W TDP SKUs, same number of cores (12). Using Cinebench R23 MT, we get:

R7 3900X: 21507 CB

R7 7900X: 28655 CB

-------------------------------

+33%

So two different sets of nodes, 2 sets of like SKUs that had similar claimed IPC uplifts (15% & 13%) yielded a 33.5% MT gain when jumping up one full TSMC node. If we apply that same logic to Zen 6's 2 full node jump and slightly lower leaked IPC target (10%), you get: 1.3 x 1.3 = 1.69 or +69% MT from Zen 5.

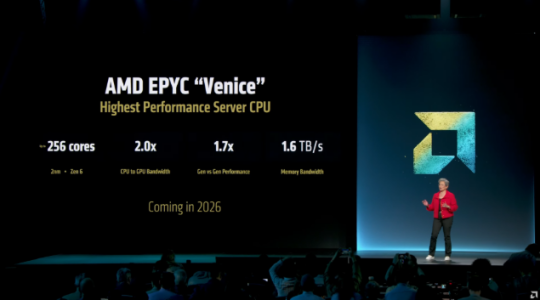

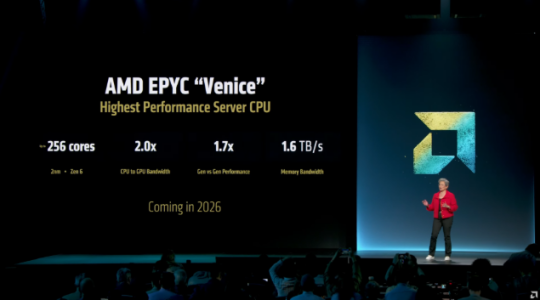

Now, we already have an official claim from Lisa Su that Venice gets a 70% uplift from Turin. This is interesting as its very close to the extrapolated figure above. Assuming this +70% is for the new 256 dense core vs the old 192 dense core, its not quite as apples to apples a comparison as my same core count SKU figures above. Further assuming that at least this is at the same TDP or electrical power as the SKU to which it is compared is helpful.

In any case, I would conclude that Zen 6 is at the very least likely going to get a >50% uplift vs same core count SKUs vs Zen 5, and potentially 70% or more in SKUs that get increased core counts, like a 16 core 9950X vs a 24 core 11950X.