marees

Platinum Member

...Verano is _NOT_ the successor to Venice, it is a Venice variant.

Florence is Venice+1 ...

Florence is Venice+1 ...

All in all, I think that the new IOD and faster memory speeds are going to be the biggest improvements we see in Zen 6 platforms next year.

I am actually not expecting much in the way of IPC of Zen 6 over Zen 5 (10-15%) and little or no increase in clock speed. In more bandwidth limited operations (likely in DC applications / HPC /AI) much larger increases in performance will be seen than the IPC bump. At a minimum, we can expect the larger core counts will result in higher performance. The IPC and bandwidth increases would then be on top of that.

Zen 6 Venice should be a very powerful platform indeed.

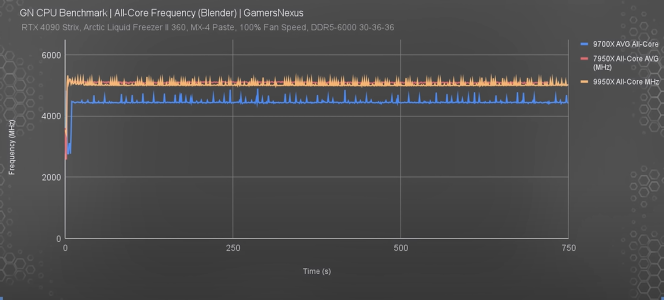

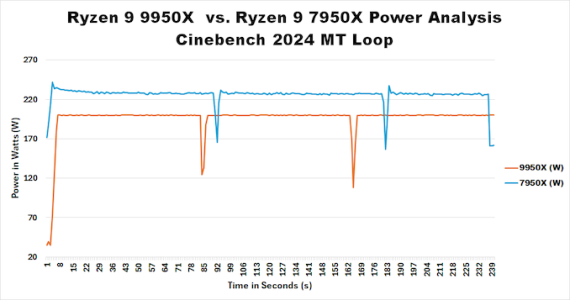

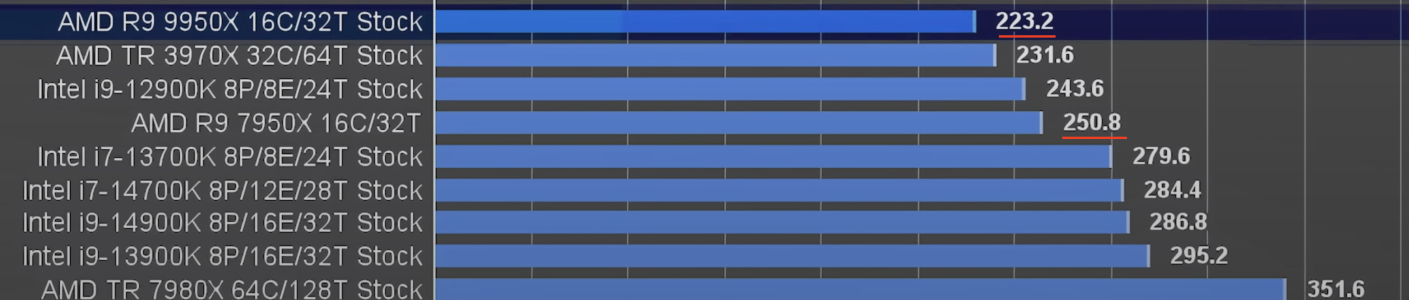

Out of curiosity, at what power limits?than current 4nm Zen 5, which actually clocks lower than Zen 4 in all core R23 runs.

I think if both are limited to 230W, I think 9950X limits to around 150- 200MHz per core lower compared to 7950X in R23 or R24. I dont know the exact numbers, and it depends on the workload, but its at least a bit lower across the board.Out of curiosity, at what power limits?

That's the thing that gets people tripped up with Granite Ridge: the PPT no longer follows the 1.35*TDP "rule". The 9950X PPT is 200w. Hence the ~100 MHz lower clock speeds.I think if both are limited to 230W, I think 9950X limits to around 150- 200MHz per core lower compared to 7950X. I dont know the exact numbers, but its lower.

I cant find a good R23 or R24 comparison now , but I could have sworn that Zen 5 boosts a bit lower even if set to the same 230W PPT.That's the thing that gets people tripped up with Granite Ridge: the PPT no longer follows the 1.35*TDP "rule". The 9950X PPT is 200w. Hence the ~100 MHz lower clock speeds.

View attachment 125761

edit: removed the wrong ppt image

The biggest improvement for desktop Zen6 over Zen 5 will be the foundry node. Going from N4P to N2P is a big jump in area inside the node triangle (efficiency, performance, density). This should lead to considerably gains in efficiency with respect to watts consumed at a given clock frequency over time. That typically translates to a big jump in MT performance due to higher sustained clocks across all active cores. So long as they aren't memory bandwidth bound, MT tasks should improve well.Absolutely. Of course, for many of the benchmarks being quoted, the transfers are artificially large in order to explicitly ensure that it will come from main memory.

In real world applications, I think that this is rarely the case and quite a bit of memory access is kept local within one of the levels of cache thus preventing a main memory access. Additionally, the specific memory elements in cache are frequently accessed repetitively.

All in all, I think that the new IOD and faster memory speeds are going to be the biggest improvements we see in Zen 6 platforms next year.

I am actually not expecting much in the way of IPC of Zen 6 over Zen 5 (10-15%) and little or no increase in clock speed. In more bandwidth limited operations (likely in DC applications / HPC /AI) much larger increases in performance will be seen than the IPC bump. At a minimum, we can expect the larger core counts will result in higher performance. The IPC and bandwidth increases would then be on top of that.

Zen 6 Venice should be a very powerful platform indeed.

Then the AMD engineers can take a vacation until Zen7. 😉The biggest improvement for desktop Zen6 over Zen 5 will be the foundry node.

Are there any credible sources claiming that it will use N2P for desktop? I think its more possible that desktop could use N3P or N3X?The biggest improvement for desktop Zen6 over Zen 5 will be the foundry node. Going from N4P to N2P is a big jump in area inside the node triangle (efficiency, performance, density). This should lead to considerably gains in efficiency with respect to watts consumed at a given clock frequency over time. That typically translates to a big jump in MT performance due to higher sustained clocks across all active cores. So long as they aren't memory bandwidth bound, MT tasks should improve well.

I agree; however, I think you will find that the vast majority of forum members believe it will be N2.Are there any credible sources claiming that it will use N2P for desktop? I think its more possible that desktop could use N3P or N3X?

Yeah.Are there any credible sources claiming that it will use N2P for desktop?

No.I think its more possible that desktop could use N3P or N3X?

Who? What about N3P? Just Instinct GPUs?Yeah.

No.

I've said like a billion times that poverty Zen6 is N3p.What about N3P

'a' GPU.Just Instinct GPUs?

Makes sense. Don't see why they would skip N3P for N2 if the former is a lot cheaper for them. It's not like they face any serious threat from Intel.I've said like a billion times that poverty Zen6 is N3p.

It's not really cheaper, just a volume utilization thing.Don't see why they would skip N3P for N2 if the former is a lot cheaper for them

Who? What about N3P? Just Instinct GPUs?

everyone will be.AMD will be a big customer of N2 wafers.

Link?Yeah.

MS themselves counted on it being Z6 based when the FTC docs leaked a few years back, so I'm giving it 95% of being a Z6 derivative.

Details of PS5 low power mode as leaked by MLID

Here are the specs revealed about the PlayStation 5 Low Power Mode (according to the leak):

- Limits CPU usage to 8 threads

- Cuts 3D audio processing power to 75%

- Clocks down GDDR6 memory to half speed

- Reduces core (CPU/GPU) clocks by about 10–20%

- Sets GPU to the minimum frequency needed for compatibility

- Limits the console to 36 Compute Units

- No PSSR (PlayStation Spectral Super Resolution), or VR support in this mode

PlayStation 5 Leak Reveals New 'Low Power' Mode, Fueling Handheld Console Reports

A new leak suggests Sony is rolling out a "low power" mode for the PlayStation 5 and PlayStation 5 Pro to developers, with ongoing rumors about a PlayStation handheld console in the worksthegamepost.com

no.I wonder if it is going to be chiplet based...

Completely different product categories.Something along the lines of LPDDR6 Medusa Halo might be ideal for consoles, but the cost may be too high...