Hulk

Diamond Member

Again, this was in reference to 285K and 9950X comparison where ST clocks are the same. They diverge as cores are loaded.Both are quite important. For client, it is ST boost clock that disproportionately affects the performance.

Again, this was in reference to 285K and 9950X comparison where ST clocks are the same. They diverge as cores are loaded.Both are quite important. For client, it is ST boost clock that disproportionately affects the performance.

Way different design methodologies.Interesting that the newer Intel CPUs (MTL, LNL, PTL, ARL) all have either same or lower clock speeds compared to years old ADL, RPL. While moving to better process nodes.

Needing 1.21 gigavolts to hit 5.7 on N3 is also historically bad.It's possible, but it would be a historically bad.

Almost like the haven't yet got to grips with eeking out the best of external nodes because they're having to learn what other companies already know. Maybe they'll get better. Need to learn to be fast, fast though. AMD knows how to do this very very well.Interesting that the newer Intel CPUs (MTL, LNL, PTL, ARL) all have either same or lower clock speeds compared to years old ADL, RPL. While moving to better process nodes.

everything pre-UC is garbage.Almost like the haven't yet got to grips with eeking out the best of external nodes because they're having to learn what other companies already know. Maybe they'll get better. Need to learn to be fast, fast though. AMD knows how to do this very very well.

Caching might drive performance with RAM at the ridiculous prices. Of course every reviewer has buttloads of RAM rather than accurate reflections of Joe Consumer.

Pentium 4 to Core / Core 2?When's the last time a new intel core lost 10%+ frequency iso-node?

Good call 😉.Pentium 4 to Core / Core 2?

It's not about what they do, it's what they don't.Still, your general assertion is correct. It is possible that NVL does more with less, and that this is a good thing all the way around. That is certainly how Core/Core 2 worked out.

LNC is kinda smol though (on the logic front)everything pre-UC is garbage.

UC is a do or die moment, they gotta fix their logic/phys-des by UC or they're toast.

Maybe they deserve a bit of leeway given that's the first core with the new phys des, n3b was apparently kinda scuffed, etc etcNeeding 1.21 gigavolts to hit 5.7 on N3 is also historically bad.

frfrBoth are quite important. For client, it is ST boost clock that disproportionately affects the performance.

Intel 7 ultra the goatInteresting that the newer Intel CPUs (MTL, LNL, PTL, ARL) all have either same or lower clock speeds compared to years old ADL, RPL. While moving to better process nodes.

gonkObviously, but claiming that Nova Lake gets zero clockspeed increase when it's moving from N3B to N2 is tantamount to saying that Coyote Cove clocks 10% worse than Lion Cove, iso-node. It's possible, but it would be a historically bad.

My new hopium is that the core is way more power efficient and is very small, area wise.Well, it’s a new core and design compared to ARL. There’s no reason that it can’t clock the same (or even lower) on a better node. Presumably, the implication is that Intel messed up the physical design or what have you. No idea whether the 5.7GHz figure is accurate or not, to be clear.

Honestly the results are so bad I'm unsure if AMD is reporting their figures correctly or if AMD's power rails are somehow inherently better T-TThey're already paying for N3 to have the same freq as AMD at more voltage.

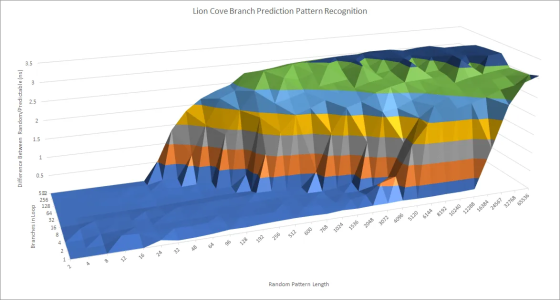

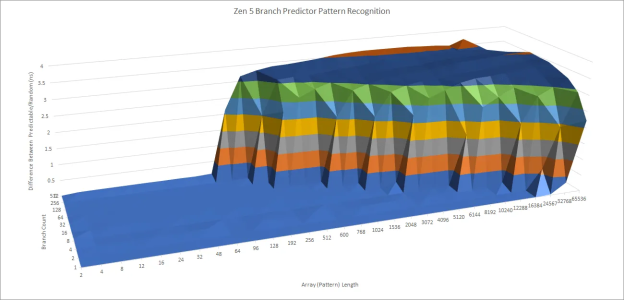

All of Zen 5's front end latency weirdness seems to be caused by the BPU.BPU no (already class-leading by a country mile),

noeperf.LNC is kinda smol though (on the logic front)

no.Maybe they deserve a bit of leeway given that's the first core with the new phys des, n3b was apparently kinda scuffed, etc etc

uh.Honestly the results are so bad I'm unsure if AMD is reporting their figures correctly or if AMD's power rails are somehow inherently better T-T

no.All of Zen 5's front end latency weirdness seems to be caused by the BPU.

yeah man pipeline flushes hurt when your L1's are tiny.Haven't seen this talked about, but Zen 5's branch mispredict penalty appears to be way higher than LNC's

you should read the chart again.And if it's true, is Zen 5 pipelined way more than LNC? Would it make sense for Intel's next gen core to clock a bit lower than AMD's one then if it just has fewer stages?

Depends a lot on 1. workload (algorithm and dataset) and 2. power limit.by the time all cores are loaded there is a 500MHz gap.

Tons of changes, also first time they moved to 2-2. I think they deserve to catch a bit of a break.

Mostly cuz ARL-H core v/f curve looks so bad, but when you look at strix point vs arl-h platform power tests they look close, if not Intel outright leading.

certainly seems that way

How does this relate?yeah man pipeline flushes hurt when your L1's are tiny.

Similar clocked products, much higher latency in ns for AMD's core?you should read the chart again.

no.Tons of changes, also first time they moved to 2-2. I think they deserve to catch a bit of a break.

N3 has Cac reduction vs N4.Mostly cuz ARL-H core v/f curve looks so bad, but when you look at strix point vs arl-h platform power tests they look close, if not Intel outright leading.

read the chart again.certainly seems that way

Pipeline flushes mean L2 fetches with tiny L1's.How does this relate?

Yes?Similar clocked products, much higher latency in ns for AMD's core?

Doesn't seem likely when NVL-S has 75% higher TDP than ORMy new hopium is that the core is way more power efficient and is very small, area wise.

I mean Intel is desperate to hit 2x nT relative to ARL-S.Doesn't seem likely when NVL-S has 75% higher TDP than OR

Absolutely, 100% true. Those TechPowerUp tests only show under default BIOS setting how high the chip will go assuming you have adequate power and cooling.Depends a lot on 1. workload (algorithm and dataset) and 2. power limit.

Furthermore, bare clock speed is not a reliable performance metric especially when more cores get utilized. Cores can clock very high if most of their cycles are spent waiting for main memory accesses instead of actually computing something.

Point is Zen(5/6) SMT results in Cinememe thread count spam.Why? It doesn't make ST perf lower. It only lowers stupid metrics no one cares about, like Cinebench points per thread.

Perf per thread does not matter for Cinebench or any other embarrassingly parallel workload.We”re talking about max MT perf, so perf/thread and thread count is what matters

As I mentioned, it’s perf/thread AND thread count. Thread count is 48T in both cases though, so that’s leaves perf/thread for comparison.Perf per thread does not matter for Cinebench or any other embarrassingly parallel workload.

Consider: if AMD adds SMT4 (lol) suddenly their perf *per thread* drops precipitously even though total throughput would likely increase. It's a useless measurement here. There is no reason to care about it for a test like Cinebench.

No it doesn't. Perf per thread is needlessly obfuscating what you actually want. Total MT throughput. You never at any point need to consider perf per thread for Cinebench.As I mentioned, it’s perf/thread AND thread count. Thread count is 48T in both cases though, so that’s leaves perf/thread for comparison.

Yes it does, since in both cases thread count is locked to 48T. So that leaves perf/thread to determine MT perf.No it doesn't. Perf per thread is needlessly obfuscating what you actually want. Total MT throughput. You never at any point need to consider perf per thread for Cinebench.

No that's a bad proxy.Yes it does, since in both cases thread count is locked to 48T. So that leaves perf/thread to determine MT perf.

Total MT throughput = Thread count * Perf/Thread