-

We’re currently investigating an issue related to the forum theme and styling that is impacting page layout and visual formatting. The problem has been identified, and we are actively working on a resolution. There is no impact to user data or functionality, this is strictly a front-end display issue. We’ll post an update once the fix has been deployed. Thanks for your patience while we get this sorted.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Question Zen 6 Speculation Thread

Page 186 - Seeking answers? Join the AnandTech community: where nearly half-a-million members share solutions and discuss the latest tech.

Josh128

Banned

Even better View attachment 126896

Brutal, and hilarious, lol.

Josh128

Banned

WTF?!! Its like the thing is actually thinking now.Yup, they are lobotomizing Grok to make sure it stays withing the guidelines issued in Tel Aviv.

**Sorry, no more OT stuff...

Josh128

Banned

Anyway back to Zen 6 what are the expectations for ST Improvement I am expecting ~1.2X.

Honestly, realistically, ~10% IPC + ~5-8% clocks. Im not expecting more than 6 GHz.

Last edited:

igor_kavinski

Lifer

Leaves plenty of room for AMD to impress us 🙂Honestly, realistically, ~10% IPC + ~8% clocks. Im not expecting more than 6 GHz.

Josh128

Banned

And hopefully not much room to disappoint 😛Leaves plenty of room for AMD to impress us 🙂

AMD has never been wafer constrained for DC. Their issues with building volume have been entirely differentKeep dreaming not happening for client as for DC we will see it took them 5-6 years to be at 40% in DC and that was with Intel screwing every time until last year which they released a DC product that is genuinely good nor AMD has a volume and are at a Volume constrained TSMC .

They will prioritize wafer for DC.

igor_kavinski

Lifer

For once, I pray that other forum members can contain themselves from hyping up Zen 6. Let's have a serene launch this time around.And hopefully not much room to disappoint 😛

I would encourage those same members to hype up Nova Lake if they want 😛

Saylick

Diamond Member

20% minimum.Anyway back to Zen 6 what are the expectations for ST Improvement I am expecting ~1.2X.

That is?AMD has never been wafer constrained for DC. Their issues with building volume have been entirely different

i've only seem CAMM memory modules hitting those speeds.

AMD helped develop MRDIMM technology, which doubles bandwidth. It doubles server DIMM bandwidth though, so it is starting at 8800, then going to 12800, then 17600. That's most likely slated for Epyc & Threadripper which would benefit both from the higher bandwidth as well as the increased capacity of the optional "tall" MRDIMM form factor.

Io Magnesso

Senior member

Still not enough...don't forget TSMC is ramping packing

Out of curiosity, do they have also highest usable bandwidth?highest Mem Bandwidth available on a server platform

Yup, they could do that. Then cut the CCD<->IOD link width in half, just for laughs 😉AMD's stretch goal should be 10,000 MT/s EXPO profile

If you are looking forward to single CCD SKU, I will also add to list a 5) wider CCD<->IOD link, otherwise your faster memory will be bottlenecked by the link.1.) 12 core CCX / CCD

2.) MT & ST freq increase due to node shrink (whatever that ends up being)

3.) Fix high idle power draw

4.) Hopefully enhanced memory controller / better 1:1 uclk/memclk speeds / CUDIMM support.

CouncilorIrissa

Senior member

Famous last words when it comes to anything client from AMD.If you are looking forward to single CCD SKU, I will also add to list a 5) wider CCD<->IOD link, otherwise your faster memory will be bottlenecked by the link.

Thunder 57

Diamond Member

2 layers X3D is like 2 X3D CCD.

Can they do it?

YES

Will they do it?

NO

I'll say it again, inter CCD latency is a thing.

that's still below from Intel's platform of 10000+ MT/s and extreme 12K+ MT/s also lets not forget ARL by default support DDR5-8000 i will expect the IMC crown with Intel this gen as well.

You just love to piss on AMD even in an AMD thread. Who cares about memory bandwith when overall performance is what matters? AMD has a dated IOD.

An L3 cache and DDR5-6000 CL24 should help things a bit. The last few halo P4 CPUs with HT could overclock to 4.25 GHz even with 65nm process. That means their double pumped FPUs were already clocking above 8 GHz. With some key inefficiencies removed, I bet engineers today could get some good mileage out of the carcass of P4 architecture.

Please stop with the P4 (expletive). You got it wrong as well. It was the ALU's that were double pumped. The P4 sucked. Stop beating the dead horse. It's already dead!

A bit OT, but about Grok, apparently X CEO stepped down today, and there is some speculation it has to do with Groks ( calling itself MechaHitler, lol) recent Hitler contraversy or the upcoming Grok4 release. 🤣 🤣

View attachment 126895

Somebody must've played Wolfenstein 3D. I was playing "Cards Against Humanity" one time around new years, and my brothers FIL thought I meant "Mega Hitler" not "Mecha Hitler". Good times.

LightningZ71

Platinum Member

I predict that mobile availability will be inversely proportionally related to the degree of performance improvement.

Makaveli

Diamond Member

Everyone that makes this request for cache on both CCD's doesn't seem to understand it does nothing to address this.I'll say it again, inter CCD latency is a thing.

Unless AMD changes how data flows in Zen 6 this is still a no.

igor_kavinski

Lifer

It could be helpful in a scenario where the cache needs are so high that evicted data is getting requested over and over again. Instead of evicting it completely, it can go into the other CCD's V-cache and reside there until needed, saving memory access latency. But yes, this is a special scenario where the other CCD isn't very busy and AMD will need to do something in hardware or driver to make this work seamlessly. Obviously won't be of any use when both CCDs are getting hammered by data hungry threads.Unless AMD changes how data flows in Zen 6 this is still a no.

Everyone that makes this request for cache on both CCD's doesn't seem to understand it does nothing to address this.

Unless AMD changes how data flows in Zen 6 this is still a no.

100%

It would take a whole new algorithm for cache coherency. Which is something that is not entirely outside of realm of possibilities, but it is not something to bank on.

One thing that changes from previous generations - accesses between IOD and CCD (and even possibly direct link between 2 CCDs) would be much cheaper from power consumption POV.

So, maybe one barrier reduced. Who knows if it is enough to open the door to a new algorithm.

Makaveli

Diamond Member

Does AMD offer this on the EPYC line don't remember if they do.It could be helpful in a scenario where the cache needs are so high that evicted data is getting requested over and over again. Instead of evicting it completely, it can go into the other CCD's V-cache and reside there until needed, saving memory access latency. But yes, this is a special scenario where the other CCD isn't very busy and AMD will need to do something in hardware or driver to make this work seamlessly. Obviously won't be of any use when both CCDs are getting hammered by data hungry threads.

But I can see it helping in maybe server and data center workloads just not helpful in general desktop and gaming workloads.

Does AMD offer this on the EPYC line don't remember if they do.

But I can see it helping in maybe server and data center workloads just not helpful in general desktop and gaming workloads.

No, it is not available in server CPUs either.

igor_kavinski

Lifer

Quoting you from the other thread because, suppose if developers got these new fangled dual V-cache CCD CPUs to tune their engines on, they could conceivably create a "pre-load" thread whose sole job would be to pre-cache stuff into the second V-cache (obviously they would use tricks since they can't directly put data into the cache). Then when the data is needed, the main thread is fed that data from the pre-load thread on the other CCD, thus mitigating the high RAM latency. Of course, this would benefit a minority of their userbase but it would be a very welcome addition to their game engine and really help in smoothing frames out.I am going to guess that majority of current game developers are now developing on X3D computers, and maybe 2-3 years down the road, that level of performance will be a requirement.

Io Magnesso

Senior member

Well, I think it's better to have less communication between CCDs.100%

It would take a whole new algorithm for cache coherency. Which is something that is not entirely outside of realm of possibilities, but it is not something to bank on.

One thing that changes from previous generations - accesses between IOD and CCD (and even possibly direct link between 2 CCDs) would be much cheaper from power consumption POV.

So, maybe one barrier reduced. Who knows if it is enough to open the door to a new algorithm.

It is better to keep that thread in one CCD

No matter how low the power consumption is, there is a reasonable cost.

Josh128

Banned

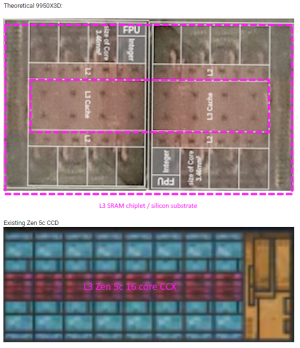

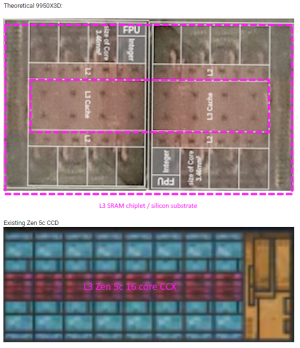

Speaking of cache coherency, reminded me of my musings about it being possible on Zen 5. Since that was a bust, maybe we can dream about Zen 6 or Zen 7?? Just add 4 cores to the CCDs shown below, put the SRAM die under both of them in a "bridge" configuration, and there you'd have it, the baddest x86 gaming CPU known to mankind.

Last edited:

TRENDING THREADS

-

Discussion Zen 5 Speculation (EPYC Turin and Strix Point/Granite Ridge - Ryzen 9000)

- Started by DisEnchantment

- Replies: 25K

-

Discussion Intel Meteor, Arrow, Lunar & Panther Lakes + WCL Discussion Threads

- Started by Tigerick

- Replies: 25K

-

Discussion Intel current and future Lakes & Rapids thread

- Started by TheF34RChannel

- Replies: 24K

-

-