DisEnchantment

Golden Member

Speculate at will

Last edited:

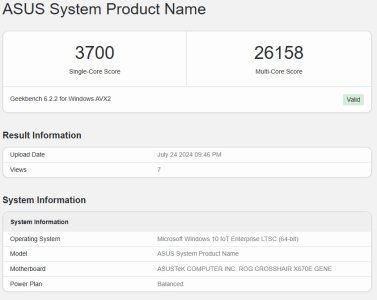

5.95 GHz, it's OC'd to hell. Someone having fun with an ES.Arrow Lake Leak got somebody excited enough to tune up a 9950X on Geekbench.

ASUS System Product Name - Geekbench

Benchmark results for an ASUS System Product Name with an AMD Eng Sample: 100-000001277-60_Y processor.browser.geekbench.com

View attachment 103765

It doesnt mater if it s too early as long as the clocks rising and falling edges are fast enough, once triggered the flip flop will keep its state for at least the duration of a clock cycle.

Same as above, if the signal is propagated swiftly this will allow for better level validation, what is a problem actually is when clocks signal hedges are not fast enough, at wich point levels coherency can no more be maintained since the flip flops cant be switched on/off correctly if the clocks signals are not well formed, no matter what are the data signals levels and shapes.

I never use such sentences, i mean such arguments or rather lack of, you know, things like "it s well known that", "it s shown in real world tests" and so on.

Make me a deal. 😉So who wants to be guinea pig and buy a CPU from the first batch now, unless AMD discloses what the actual problem was and how well it could be fixed?

You may not like that real world tests prove your theory wrong, but that is the ultimate evidence. You can theorize all you want, but if the real life tests show something very different or even the opposite, then your theory is clearly wrong. The proof is in the pudding.

Hold time violations are also called minimum delay violations because the signal is propagating too fast,

The pudding interior say that time violation occur mainly when the data signal is too late.

It can occur if the signal comes too early but in this case it s only if the clock is too high and as a consequence that there s not enough time for the stage to be triggered during the relevant clock cycle as to hold the desired value.

So assuming that frequency is low enough at the start there will be no time violation by other mean than the transistors not switching fast enough, that is, too low transconductance to charge parasistic capacitances in due time, i.e, signal being too late as a result.

Hold violation happen when data is too fast compared to the clock speed. For fixing the hold violation, delay should be increased in the data path.

*Note:* Hold violations is critical and on priority basis in comparison are not fixed before the chip is made, more there is nothing that can be done post fabrication to fix hold problems unlike setup violation where the clock speed can be reduced. The designer needs to simply add more delay to the data path.

Either that or it’s Zen 5% failure rate+32% IPC Zen5 on August 15th!!

Prove it, otherwise. . .

10 Ways to fix SETUP and HOLD violation: Static Timing Analysis (STA) Basic (Part-8)

VLSI Basics, Static Timing Analysis , Parasitic Extraction , Physical Design, DFM, Interview Questions, Resume Sample and Other VLSI Informationwww.vlsi-expert.com

It can occur if the signal comes too early but in this case it s only if the clock is too high and as a consequence that there s not enough time for the stage to be triggered during the relevant clock cycle as to hold the desired value.

So assuming that frequency is low enough at the start there will be no time violation by other mean than the transistors not switching fast enough, that is, too low transconductance to charge parasistic capacitances in due time, i.e, signal being too late as a result.

You re just repeating what i said, so how should i prove it otherwise, didnt i say that if clocks are low enough there will be no time violation..??

So read first what is said, since you re now trying to make a point out of something you once negated a few post above, your quote is saying exactly what i stated in my post that i just quoted above.

Anyway, at least i got a good pile of lols for free.

Here the quote you posted :Read it again, it agrees with me.

Hold violation happen when data is too fast compared to the clock speed. For fixing the hold violation, delay should be increased in the data path.

The pudding interior say that time violation occur mainly when the data signal is too late.

It can occur if the signal comes too early but in this case it s only if the clock is too high and as a consequence that there s not enough time for the stage to be triggered during the relevant clock cycle as to hold the desired value

Here the quote you posted :

And here what i said before you posted this quote :

So what you quoted is just the same thing as what i said, and the contrary to what you said in your first posts on the subject.

Edit : The data signal state will last as long as the clock signal doesnt change state, if the clock signal is of low enough frequency the data signal will have all necessary time to trigger the driven stage.

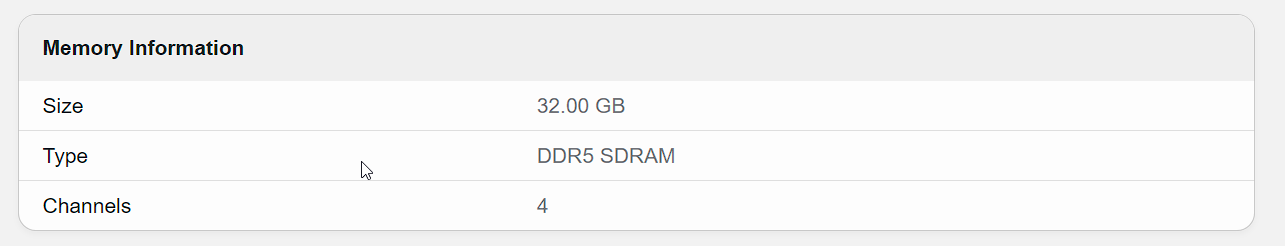

Is it a geekbench issue that it says "Memory Channels : 4"?Arrow Lake Leak got somebody excited enough to tune up a 9950X on Geekbench. Multiple different runs of 5950 MHz all core OC today, probably DI or LN2

ASUS System Product Name - Geekbench

Benchmark results for an ASUS System Product Name with an AMD Eng Sample: 100-000001277-60_Y processor.browser.geekbench.com

ASUS System Product Name - Geekbench

Benchmark results for an ASUS System Product Name with an AMD Eng Sample: 100-000001277-60_Y processor.browser.geekbench.com

View attachment 103765

From GB6.3: if it’s dual channels it will say 2.

Me. Its not a problem. READ. Its a QA issue. In other words, allowing a 9950x to be sold at under the advertised MHZ or the like.So who wants to be guinea pig and buy a CPU from the first batch now, unless AMD discloses what the actual problem was and how well it could be fixed?

that's an old 6GHz sample.Arrow Lake Leak got somebody excited enough to tune up a 9950X on Geekbench. Multiple different runs of 5950 MHz all core OC today, probably DI or LN2

Reading the other posts in this thread, it does not seem to be clear what exactly the reason for the delay is. QA could mean lots of things. How come you think it’s likely a frequency only issue?Me. Its not a problem. READ. Its a QA issue. In other words, allowing a 9950x to be sold at under the advertised MHZ or the like.

Worse case, allowing a 9950x to be sold that does not meet QA and at top frequency, is not stable. Sound familiar ?

Edit: If it was an actual issue with the chips, there's no chance they would be able to get them fixed and new ones out the door within a week or two. It would have to be either the QA testing miss as explained, or something wrong with the microcode/firmware that they could fix and push out quickly.

I wonder how that i9 14900KS is feeling. Probably in a world of pain.

These talented and highly professional people don't get it in their heads to do crazy or stupid things on the CPUs. That's how they got their job in the first place. Usually someone wanting to monkey about with things isn't tolerated at most workplaces around the world.These companies are packed with talented and highly professional people, yet things go wrong from time to time. This (Zen 4/RPC) gen should be very indicative of that.

Maybe some smartass in the art department drew a really tiny doodle on the Zen 5 IHS and one or some of the reviewers discovered it while examining the IHS with magnification. And it's probably NSFW.It’s good that AMD found this issue before launch. But as I finding this issue this close to launch is a bit concerning. AMD should have done tested all scenarios and not skipped on some.